#### University of Louisville

# ThinkIR: The University of Louisville's Institutional Repository

**Electronic Theses and Dissertations**

4-2011

## A prototype security hardened field device for SCADA systems.

Bradley Alan Luyster University of Louisville

Follow this and additional works at: https://ir.library.louisville.edu/etd

#### **Recommended Citation**

Luyster, Bradley Alan, "A prototype security hardened field device for SCADA systems." (2011). *Electronic Theses and Dissertations.* Paper 869. https://doi.org/10.18297/etd/869

This Master's Thesis is brought to you for free and open access by ThinkIR: The University of Louisville's Institutional Repository. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of ThinkIR: The University of Louisville's Institutional Repository. This title appears here courtesy of the author, who has retained all other copyrights. For more information, please contact thinkir@louisville.edu.

### A PROTOTYPE SECURITY HARDENED FIELD DEVICE FOR SCADA SYSTEMS

By

Bradley Alan Luyster B.S., University of Louisville, 2009

A Thesis Submitted to the Faculty of the University of Louisville J. B. Speed School of Engineering as Partial Fulfillment of the Requirements for the Professional Degree

## MASTER OF ENGINEERING

Department of Electrical and Computer Engineering

April 2011

## A PROTOTYPE SECURITY HARDENED FIELD DEVICE FOR SCADA SYSTEMS

Submitted By:\_\_\_\_\_ Bradley Alan Luyster

A Thesis Approved On

(Date)

by the Following Reading and Examination Committee

James H. Graham, Thesis Co-Director

Jeffery L. Hieb, Thesis Co-Director

John Naber, Committee Member

#### ACKNOWLEDGMENTS

I would like to thank Dr. Jeffery Hieb for his assistance in guiding me through the miasma of academia, as well as Jane Tanner for her invaluable advice in navigating the shores of both University bureaucracy and the greater world. I must also thank my Uncle, Bill Luyster, for providing the initial spark which eventually led me to Electrical Engineering. Finally, I cannot thank enough my parents, Thom and Wendy Luyster, for providing unflagging support, no matter what endeavor I have taken upon myself.

#### ABSTRACT

This thesis describes the development of a prototype security hardened field device (such as a remote terminal unit) based on commodity hardware and implementing a previously developed security architecture. This security architecture has not been implemented in the past due to the difficulty of providing an operating system which meets the architecture's isolation requirements. Recent developments in both hardware and software have made such an operating system possible, opening the door to the implementation and development of this new security architecture in physical devices attached to supervisory control and data acquisition (SCADA) systems. A prototype is developed using commodity hardware selected for similarity to existing industrial systems and making use of the new OKL4 operating system. Results of prototype development are promising, showing performance values which are adequate for a broad range for industrial applications.

# **Table of Contents**

| ACKNOWLEDGMENTS                                   | iii |

|---------------------------------------------------|-----|

| ABSTRACT                                          | iv  |

| CHAPTER I – INTRODUCTION                          | 1   |

| 1.1 BACKGROUND                                    | 1   |

| 1.2 PROBLEM                                       | 2   |

| 1.3 MOTIVATION                                    | 3   |

| 1.4 ORGANIZATION                                  | 3   |

| CHAPTER II – LITERATURE REVIEW                    | 5   |

| 2.1 SCADA SECURITY                                |     |

| 2.1.1 SCADA SECURITY ISSUES                       | 7   |

| 2.1.2 SECURING SCADA SYSTEMS                      | 8   |

| 2.2 ARCHITECTURAL SECURITY IN KERNEL MODELS       | 9   |

| 2.2.1 SEPARATION KERNELS AND MICROKERNELS         | 11  |

| 2.2.2 THE OKL4 MICROKERNEL                        | 15  |

| 2.2.3 THE SEL4 KERNEL.                            |     |

| 2.3 A SECURE INDUSTRIAL SYSTEM USING MICROKERNELS | 19  |

| CHAPTER III – DESIGN APPROACH                     | 21  |

| 3.1 ARCHITECTURE MODEL AND SECURITY FEATURES      | 21  |

| 3.2 PRIOR WORK                                    | 25  |

| 3.3 ISOLATING COMPONENTS WITH CELLS AND THREADS   |     |

| 3.4 INTER-CELL COMMUNICATION USING IPC            | 29  |

| 3.5 SECURITY FEATURES                             | 34  |

| 3.5.1 A SIMPLIFIED SCADA PROTOCOL                 |     |

| 3.5.2 USER AUTHENTICATION AND HANDSHAKING         | 40  |

| 3.5.3 ROLE BASED ACCESS CONTROL                   | 41  |

| 3.6 DESIGN SUMMARY                                | 43  |

| CHAPTER IV – IMPLEMENTATION.                      |     |

| 4.1 HARDWARE, BUILD SYSTEM, AND WORKFLOW          | 44  |

| 4.2 IO HARDWARE AND SOFTWARE                      |     |

| 4.3 UTILITY FUNCTIONALITY                         | 55  |

| 4.3.1 HARDWARE MANAGEMENT                         | 56  |

| 4.3.2. SERIAL DEBUG                               |     |

| 4.4 NETWORK IO                                    |     |

| 4.5 SECURITY CELL                                 |     |

| CHAPTER V – PERFORMANCE ANALYSIS                  |     |

| 5.1 TEST GOALS AND CONSTRAINTS                    |     |

| 5.2 TEST METHODOLOGIES                            |     |

| 5.3 INITIAL PERFORMANCE MEASUREMENTS                        | 70   |

|-------------------------------------------------------------|------|

| 5.4 SECURITY FEATURE PERFORMANCE MEASUREMENTS               | 73   |

| CHAPTER VI – CONCLUSIONS AND FUTURE RESEARCH                | 76   |

| 6.1 SUMMARY OF RESULTS                                      | 76   |

| 6.2 FUTURE DIRECTIONS                                       | 78   |

| REFERENCES                                                  | 81   |

| APPENDIX I – LAB MANUAL                                     | 83   |

| APPENDIX II – SELECTED CODE                                 | 95   |

| APPENDIX 2.1 – UTILITY CELL ELFWEAVER XML FILE              | 95   |

| APPENDIX 2.2 – DATA STRUCTURES IN ROLE-BASED ACCESS CONTROL | . 95 |

| APPENDIX 2.3 – PHYSICAL IO INTERFACING                      | 97   |

| VITA                                                        | 99   |

|                                                             |      |

#### GLOSSARY OF TERMS

- Capabilities A security construct which contains both the reference required to access an object, as well as access rights assigned to the capability holder. Ownership of a capability implies permission to access a given resource.

- Cell A virtual construct in the OKL4 operating system. A logical set of a running thread, a memory space, and a zone.

- Dnp3 Distributed Network Protocol, a common communication protocol in industrial control systems.

- I2C Inter-IC bus

- IDE Integrated development environment

- IPC Interprocess communication

- Kernel An operating system's lowest level abstraction code, interfacing between hardware and application code, often performing other duties such as memory management, task scheduling and file system management, among others.

- MTU Master terminal unit

- Macrokernel An operating system kernel which places code such as file system management, device drivers, and server daemons in kernel-mode code.

- Memory space An OKL4 construct which separates a given section of virtual memory from all other sections of virtual memory.

- Microkernel An operating system kernel which seeks to minimize code which runs in kernel-mode.

- Modbus A common communication protocol used in industrial control systems.

- OKL4 A commercially available microkernel operating system, currently the primary focus of research on the L4 family of microkernels.

- Points A distinct input or output on a field device. Examples include digital inputs and analog outputs.

- Pre-shared Secret a secret shared previously shared between two systems using a secure communications channel, used for authentication and verification of credentials.

- RBAC Role based access control

- RTU Remote terminal unit

- RPC Remote procedure call

- SCADA Supervisory control and data acquisition

- SDK Software development kit

- SHA-256 A cryptographic hashing function which encodes a given set of data as a unique 256 bit value.

- TFTP Trivial file transfer protocol

- TCP Transmission control protocol, a core protocol of the Internet protocol stack.

- Thread A piece of code executing concurrently with other pieces of code, switched in and out in a "timesharing" manner.

- UDP User datagram protocol. A simpler alternative to TCP which sacrifices reliability for speed and simplicity.

- XML Extensible markup language

- Zone A construct in OKL4 defining which memory spaces may access each-other.

## LIST OF TABLES

| Table 2.1: Cost of Minimal L4 IPC Transfer on Various Architectures         [28] | 18 |

|----------------------------------------------------------------------------------|----|

| Table 3.1: Summary of Simplified SCADA Communications Protocol                   | 37 |

| Table 5.1: IPC Performance measurements                                          | 71 |

| Table 5.2: Performance Summary of Security Operations                            | 74 |

## LIST OF FIGURES

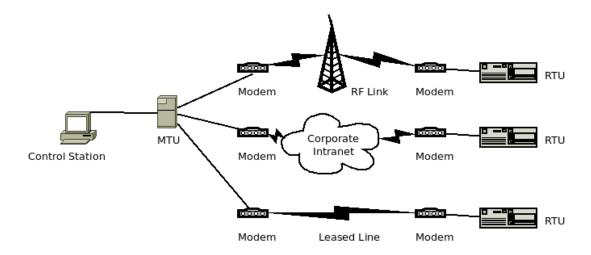

| Figure 2.1: Typical SCADA System Architecture                                      | 6  |

|------------------------------------------------------------------------------------|----|

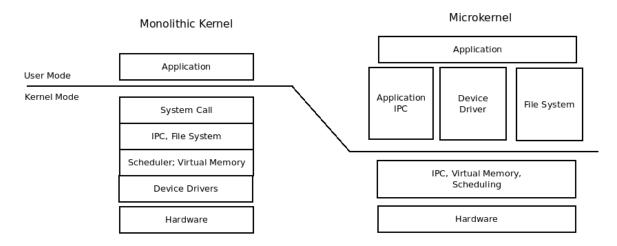

| Figure 2.2: Monolithic and Micro- Kernel Architectural Differences                 | 11 |

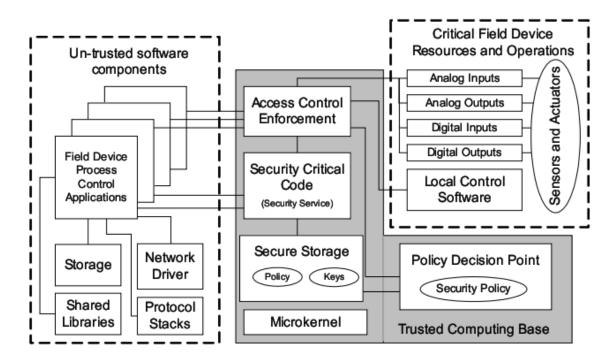

| Figure 3.1: Target Architecture from [33]                                          | 22 |

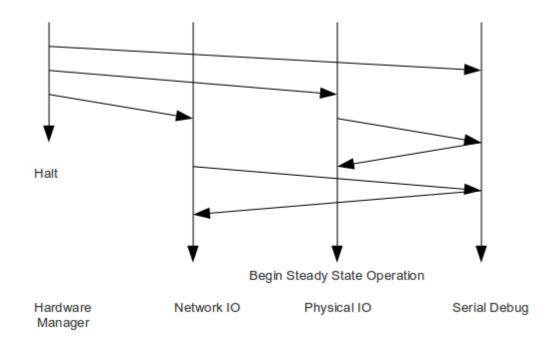

| Figure 3.2: IPC messages during Start-up                                           | 31 |

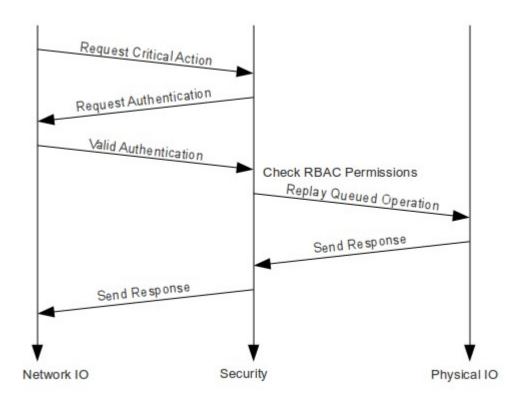

| Figure 3.3: IPC from Network Event to Physical IO, given proper RBAC credentials   | 32 |

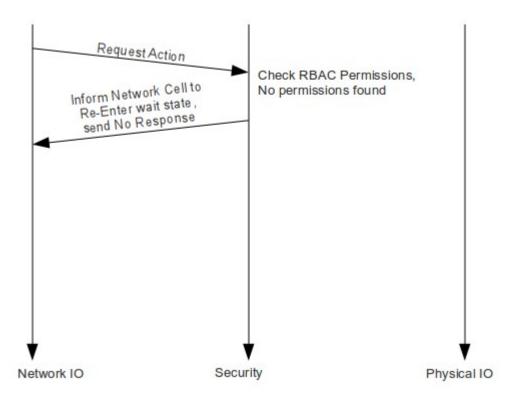

| Figure 3.4: IPC from network event to physical IO, given improper RBAC credentials | 33 |

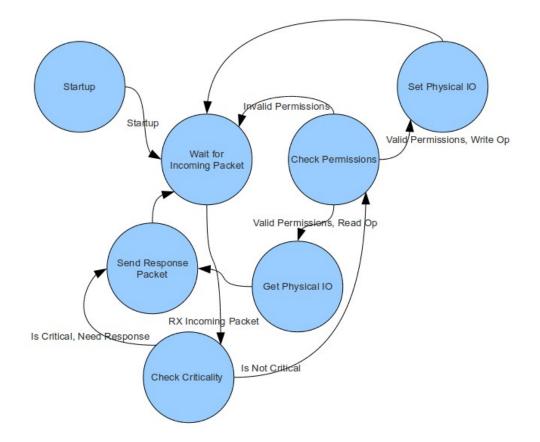

| Figure 3.5: Full state diagram for IPC                                             | 34 |

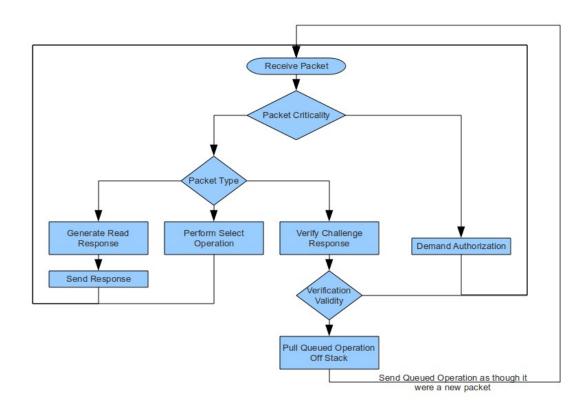

| Figure 3.6: Decision tree for SCADA packet reception                               | 39 |

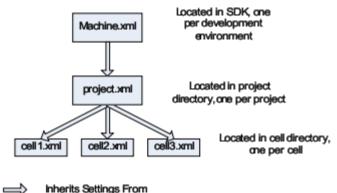

| Figure 4.1: Hierarchy of ElfWeaver Compilation                                     | 48 |

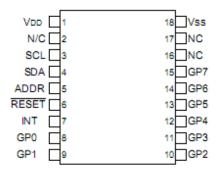

| Figure 4.2: Pinout of theMCP23009 Digital IO IC                                    | 50 |

| Figure 4.3: Pinout of the MCP4725 Analog Output IC                                 | 51 |

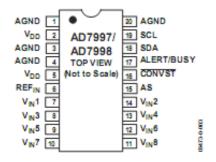

| Figure 4.4: Pinout of the AD7997 Analog Input IC                                   | 51 |

| Figure 5.1: IPC Communications Testing Paths                                       | 70 |

#### **CHAPTER I**

#### **INTRODUCTION**

This thesis describes the design, development, and testing of a security hardened field device, such as a remote terminal unit (RTU) for supervisory control and data acquisition (SCADA) systems. This prototype RTU is developed using several previously researched, but as-of-yet unconstructed, architectural features which are designed to provide additional layers of security to industrial control systems which control this nation's energy, water and fuel supplies (among many other systems). This thesis will review the pitfalls of existing SCADA systems, explore the possibilities of security hardened systems using new architectural structures, and describe the development and testing of a prototype RTU utilizing these structures.

#### 1.1 Background

SCADA systems are used in the operation of many industrial systems, from the power grid to potable water distribution: large, monolithic systems which are critical to the health and well-being of the citizenry. These systems are widely distributed, and require a large number of remote terminals, each controlling a small number of devices, and gathering data from a small number of sensors. Many of these systems are connected to a central control location by a variety of possible commodity communications systems, ranging from radio links to industrial Ethernet connections. Unfortunately, as these systems have grown larger, the pervasiveness and public awareness of these commodity communications systems has also grown. Corporations and utilities can no longer rely on security through obscurity to protect these systems. Further, with the growth of the

Internet, these systems have become increasingly connected, forcing industries to defend against security threats well outside these systems' design parameters.

Network security and an understanding of these communications problems can only provide a modest amount of security. Drop in modules can provide additional security, but these control systems have product lifetimes measured in decades. The security solutions used in these modules may find themselves outmoded or broken in a few months or years, becoming a huge expense to any company maintaining a device's security.

#### **1.2 Problem**

Part of the security problem is endemic to the architecture utilized by these devices. The monolithic kernels used by the operating systems integrated into the RTUs currently on the market are fundamentally incapable of providing the high assurance security required of such critical control devices. Formal verification is a key component of high assurance systems. For many years, this verification has been out of reach for operating-system kernels. Several operating systems since the 1970's have attempted to claim the crown of verified security, and several certifications exist which provide some subjective measurement of security. For many systems, these measures are sufficient – such operating systems are used in the aerospace and defense industries.

Due to the important role kernels play in providing device security, building an RTU with high assurance requires the use of a trusted kernel. A verified operating system allows for the development of verifiable security structures. If these structures operate as intended, then a deterministic level of security can be architected, transcending the

security of any drop-in device or network security solution. As a result, it is possible to create an RTU whose security is absolutely guaranteed over the lifetime of the device.

#### **1.3 Motivation**

The creation of a prototype would be impossible without the existence of a verified secure operating system. Until now, many architectures for verified operating systems have been proposed, and many have endured rigorous testing and certification procedures, only to fall just short of completely verifiable performance. Recently, a research group in Australia has reportedly achieved the rigorous mathematical verification of a microkernel based operating system. Using this operating system, a prototype can be developed using previously researched architectures, and its performance measured in order to determine the viability of such an architecture implemented with modern hardware and software. A security architecture developed by Hieb and Graham [33] considers the features provided by a microkernel operating-system, and the possibilities of a formally verified kernel. Until the development of this new kernel, the implementation of a prototype based on this architecture has been impossible.

#### 1.4 Organization

The second chapter of this thesis presents a detailed review of related literature and research, more clearly defining and developing the summary provided in this chapter. Chapter three presents the design architecture, explores the security features developed in prior work, and examines how such an architecture can be applied to the verified operating system. Chapter four is an in-depth exploration of the development environment and the prototyping process, reviewing the implementation of the prototype from hardware to software. Chapter five describes the methods and results of performance testing the RTU prototype. Chapter six summarizes the findings of this thesis, and explores some possible future directions for continued research in this area.

#### **CHAPTER II**

#### LITERATURE REVIEW

This review of existing literature provides an overview of the current state and history of SCADA security research. The following sections will detail the work and research which has led to the need for the development of a prototype as described in the following chapters. Section 2.1 provides an overview of SCADA systems and their associated security deficiencies. Section 2.2 examines the insufficiencies and failures of existing solutions. Section 2.3 explores separation and microkernels in the context of security solutions, and Section 2.4 explores the existing work done in using microkernels in industrial systems.

#### 2.1 SCADA Security

Supervisory Control and Data Acquisition (SCADA) is a term that has come to refer to any and all devices involved in a computerized, automatic industrial control system. The IEEE defines SCADA systems as "A system operating with coded signals over communication channels so as to provide control of remote equipment (using typically one communication channel per remote station). The supervisory system may be combined with a data acquisition system, by adding the use of coded signals over communication channels to acquire information about the status of the remote equipment for display or for recording functions[2]." These systems rose to prominence concurrent to microcomputers, beginning in the 1960s. As SCADA became more popular, the different architectures used became codified in IEEE Standard C37.1-2008 [3].

Principally, there are three different SCADA system architectures, the first two being primarily of historical interest.

Figure 2.1: Typical SCADA System Architecture

Initially, SCADA systems were completely centralized, with a single master controller station connected directly to sensors, actuators, and other intelligent electronic devices (IEDs). These systems had no connectivity to a greater network of sensors or devices. Eventually, these SCADA systems developed into decentralized systems, with one or more master terminal units (MTUs), and one or more remote terminal units (RTUs) [4]. These RTUs were connected to a larger network of MTUs using proprietary, industrial communication links. Following a period of decentralization in SCADA architecture, these networks transitioned from using proprietary hardware, software and communication links, to using commodity, commercial and public hardware, software and communications links, gaining larger connectivity to a network of SCADA devices. These networks gradually became integrated with larger corporate intranets, and the Internet [5].

As these SCADA networks became part of a larger network of standardized hardware and software, the communications protocols used were also standardized. The amount of information that these early links were able to carry limited the amount of information that could be expressed using these protocols. As a result of the initially proprietary nature of the links, the bandwidth limitations of the links, and the real-time nature of the processes being controlled by SCADA systems, these protocols were not designed with any built-in security features. The protocols currently in broad use, including ModBus, and IEC 60870-5-101 do not include any inherent security features, while DNP3 includes provisions for security which remain in draft form [6, 7].

#### 2.1.1 SCADA Security Issues

SCADA security hasn't been a large concern through the history of SCADA systems. SCADA systems initially used proprietary hardware and software on closed networks. As a result, security was provided by the obscurity of the system, and the lack of general knowledge as to how these systems operated. As a result, a majority of SCADA security threats came from employee sabotage. As SCADA system have shifted from obscure, closed systems, to open, commodity-based systems on open networks, the attack vectors have appropriately shifted. A study conducted by Byres and Lowe in 2003 found that attacks from insiders represented 38% of SCADA security breaches in 2000, with external attacks accounting for 31%, while in 2003, internal attacks represented only 5% of security breaches and external attacks accounted for another 70% [8].

In summary, network connectivity and standardization has infiltrated the industry in a bid to increase awareness and control. While this has decreased costs, it has also resulted in the pervasive distribution of SCADA systems which are susceptible to electronic attack [9]. In addition to using hardware and software which contains known and unknown vulnerabilities, the documentation for these systems is now freely available [10], showing that security through obscurity is no longer a trustworthy method for maintaining the integrity of SCADA networks.

#### 2.1.2 Securing SCADA Systems

With the general acceptance that SCADA systems have inherent insecurities which are acting as vectors for outside attack, it is crucial that strategies be developed in order to solve these problems. Because of the commodity hardware being used in these SCADA networks, many sources suggest using common information technology (IT) based security practices, such as enabling WEP on wireless devices [11], increasing network connectivity in order to provide more resiliency to attack [10, 11], implementing role based access control [12], and segmenting the SCADA networking using firewalls and virtual private networks [10, 11, 13].

While these methods provide some security, they are insufficient by themselves. They fail to properly differentiate between the security needs of a SCADA control network and a typical corporate network. Although the resources used in creating and managing these SCADA networks are increasingly similar to the solutions used in traditional corporate IT environments, these solutions fail to understand the key differences between SCADA systems and IT based systems.

SCADA systems require high data integrity, high up-time and high security at all points in the network. If any leaf of the SCADA network (any RTU, or MTU sub-tree)

fails, then the entire SCADA system may have its operation compromised. The IT based solutions focus on high data throughput, with a tolerance for data corruption or loss, and principally focus on the confidentiality of data. As a result, adopting these IT based solutions in a SCADA environment can be costly, and may not provide the necessary protection. IT based solutions generally focus on making the core of the network secure, reliable, and robust, while security among the leaves of the network is allowed to languish. In the SCADA network, this cannot be tolerated because the leaves of the network connect to physical control systems. Unfortunately, the vast majority of the solutions being deployed and developed today focus on these IT based solutions.

Other systems architectures advocate securing the communication links between SCADA devices with drop-in encryption modules [14]. These modules provide a reasonably high level of protocol-layer security without adversely affecting performance, as the IT based solutions might. Unfortunately, these modules only encrypt the communication link, and do not guard against vulnerabilities in the hardware or the commodity operating systems running on these SCADA devices. Furthermore, these devices add a focus on data confidentiality, while data integrity is usually a higher priority for SCADA: an attacker need only understand that these link encryption modules block intrusion at only one layer of the SCADA system stack.

#### 2.2 Architectural Security In Kernel Models

Unfortunately, the basic design architecture of using off-the-shelf operating system software adds an inherent level of risk to the system in question. Traditional operating systems are hugely complicated pieces of software. The operating system itself

can be logically divided into the sections which operate in user mode, and the sections which operate in kernel mode. The sections which operate in kernel mode provide direct abstractions to the hardware that the operating system is running on. As a result, the kernel mode code has special access to the hardware of the system, and operates without the safety of memory segmentation and protection. The kernel mode code of any operating system must be part of that system's trusted code – that is, the kernel mode code must be trusted to perform its duty with certainty and integrity.

Unfortunately, the majority of commodity operating systems today use a monolithic kernel architecture, including massive amounts of code in the kernel of the operating system, such as file system code, device driver code, and many many other services. The Linux kernel, as of version 2.6.35, contained over 13.55 million lines of code[15]. Some sources estimate the number of lines of code in Windows XP at 40 million[16]. More code is a direct vector for taking advantage of a system. Hackers with an understanding of the systems being used can exploit bugs, both known and unknown, and larger systems inherently contain more bugs. Various sources place the average number of bugs in a given piece of code between 2 and 75 bugs per 1000 lines of code. [17, 18]. Even conservative estimates at the number of errors in a code-base this large place the number of bugs in the tens of thousands. As a result, there are inherent insecurities and instabilities in operating system kernels of this magnitude.

#### 2.2.1 Separation Kernels And Microkernels

There is an alternative to this monolithic kernel architecture. A microkernel is a kernel architecture which seeks to provide minimal kernel level abstractions to the hardware of a given platform. As a result, these kernels provide minimal services, and force items like file systems and device drivers to operate in user mode, without privileged access to all the resources of a system.

Dr. Jochen Leidtke formalized this concept of minimalist design thusly:

A concept is tolerated inside the microkernel only if moving it outside the kernel, i.e., permitting competing implementations, would prevent the implementation of the system's required functionality.[19]

As a result, modern microkernels provide very few services familiar to monolithic kernels. Figure 2.2 shows some of the differences between monolithic kernels and microkernels.

Figure 2.2: Monolithic and Micro-Kernel Architectural Differences.

In Liedtke's implementations, these services were limited to management and protection of memory spaces; thread creation, destruction, management and scheduling; interrupt management; and inter-process communication. Due to these cutbacks, a microkernel can be implemented in under ten thousand lines of code. This immediately reduces the number of possible bugs which can be used as an attack vector by several orders of magnitude. Additional services must be implemented in user-mode, but much of this code need not operate in a completely error-free manner in order to provide a secure system. Tanenbaum, original author of the MINIX operating system, advocates the implementation of microkernels as the basis of a secure and reliable system[20].

Although the concept of placing critical operating system services in user space has existed since at least the 1960s [21], UNIX and BSD remained the dominant operating systems of the era, and these operating systems made a design decision to place services such as device drivers and file systems in the kernel. As a result of the popularity of UNIX and BSD, many other operating systems followed suite in this monolithic design.

In the 1970's, Tymshare Inc. began development of a new operating system called GNOSIS, (The Great New Operating System in the Sky) which would evolve into KeyKOS, and later EROS, as the concept and source code were bought and sold. The EROS operating system, a self-claimed "nanokernel" operating system, was designed to be an extremely reliable and secure operating system. This operating system provides security and separation through the communication of "capabilities." These capabilities are unforgeable representations of the rights which a program has for a specific operating-

system object. Although the foundations of EROS were laid in the 1970s, development and implementation of these concepts took place primarily in the late 1980s and early 1990s. EROS has two successor projects, CoyotOS and CapOS. These projects are lead by two of the principal developers of the EROS project. As of 2010, development for both these projects remain inactive. Despite being proclaimed a "nanokernel," the source tree for the final release of EROS is over twice as large as modern microkernels.

To block all layers of possible intrusion, an operating system known as a "separation kernel" was proposed as early as 1981 by Dr. John Rushby [22]. This kernel would treat software components as if they were pieces of a physically distributed system. Each piece of software must have no interaction with software extant to itself, save for a known quantity of communication paths. Thus, the flow of information between components of a separation kernel system may be completely known. As of 2010, only a single separation kernel has received any sort of formal certification [23].

In 1984, development began on the Mach kernel at Carnegie Mellon[24]. This kernel is one of the first examples of a kernel designed with microkernel principals throughout. Unfortunately, the purpose of this kernel was to support operating system research, primarily in the areas of parallel and distributed computing. As a result, this kernel was not designed with minimality and security in mind, but rather sought to emulate the UNIX kernel in whole. As a result, the source tree became extremely large, the result of attempting to fit monolithic kernel attributes into the microkernel architecture. Additionally, during the early 1990s, CPU speed grew at over 60% per year, while memory speed grew at only 7% during this same period. The necessity of

switching in and out of kernel mode in order to perform routine microkernel tasks like memory space management and interprocess communication requires more access to memory than a comparable monolithic kernel. As a result of this rising difference between CPU and memory speed, performance of microkernels waned. Between the increasing size of code, and the waning kernel performance, the interest in microkernels spurred by Mach and other projects declined.

Roughly concurrent to the development of the Mach kernel, Tanenbaum released MINIX, a microkernel operating system designed to be a minimal implementation of a UNIX operating system. This operating system was designed to be a companion for a textbook on operating systems. As a result, security and minimality were not design goals. The first version of the operating system, however, was implemented in only 12,000 lines of code, which is comparable with modern microkernels.

The QNX operating system is another example of a microkernel based operating system. This operating system began as a research project at University of Waterloo in 1980. This project has evolved, and changed hands many times, however. Some versions of the QNX operating system have been available as open-source products, while others have not. The most recent version, which has received a certificate of security evaluation, is currently closed source and owned by Research in Motion[25]. QNX has seen used in many high reliability systems. Although this operating system has been proven commercially, and achieves similar performance to the L4 Microkernel, its certificate of verification is based on informal criteria of evaluation.

Following the decline of the Mach microkernel, Liedtke began research on a new

generation of microkernels. Throughout the mid 1990s, until his death in 2001, Leidtke developed several new microkernel paradigms that would prove that microkernels were not required to perform badly [21, 26]. The L3 and L4 microkernels achieved their performance goals by tightly coupling the algorithms used to perform memory space management and IPC to the target system architecture. Earlier work had focused on creating a microkernels which weren't bound to a specific set of hardware, as well as creating a kernel which could place important services in user mode. Liedtke's kernels were the first to be designed specifically with performance in mind. The L4 operating system was written primarily in assembly language and C. Porting this operating system to other architectures was a daunting task. The L4::Hazelnut project was the first to successfully translate the L4 operating system into C++ without a great performance penalty. The L4::Pistachio project would further build on the success of the L4 kernel, and generalize the architecture specific algorithms and programming interface, decoupling the kernel code from the target architecture, with the exception of only a few required assembly-language function implementations [29].

#### 2.2.2 The OKL4 Microkernel

The OKL4 Microkernel is a descendant of the L4::Pistachio kernel, implementing a capability based security system similar to the one implemented by EROS. This microkernel is a good example of a third-generation microkernel [27]. In order to more fully explain the operating principals of a modern microkernel, OKL4 will be used as an example. The current version of OKL4 is Version 3.0, and is available as open-source software from NICTA. The OKL4 microkernel, as a direct descendant of Liedtke's L4 kernel, implements minimal operating system abstractions, including memory space management, thread management, and interprocess communication (IPC). Additionally, the OKL4 kernel exports management of kernel resources to user mode processes using a modified, simplified capability system from the EROS operating system. These capabilities represent a non-forgeable token of an object, as well as the program's permissions to operate on or with the object. As a result, memory spaces, thread, and IPC can be controlled from user mode processes with a measurable assurance of security [28].

In the OKL4 operating system, threads may have one or more memory spaces mapped to them. These memory spaces present themselves as virtual memory to the thread. This virtual memory, however, must be backed by physical memory allocated to the OKL4 kernel or a delegating user-mode program. The specific mapping of this memory is known only to the kernel, or a user-mode memory delegation implementation. As a result, in order to learn about this specific memory mapping, a thread must have appropriate capabilities, ensuring that threads cannot inspect or modify memory to which they have no capabilities. Threads are switched in a round-robin fashion, based on priority.

Interprocess communication (IPC) is the basis of interrupt management, remote procedure call (RPC) implementations, and data transfer between threads. In OKL4, IPC is abstracted depending upon its specific use. In all cases, in order for IPC to take place, the communicating cell must have capabilities to the recipient cell. If so desired, the communicating cell can transmit temporary "reply" capabilities to the recipient cell in order to receive a response. These reply capabilities are temporary. If IPC takes place between threads in the same memory space, then a full kernel-mode switch need not occur, saving CPU cycles. If an IPC takes place between threads existing in different memory spaces, then the OKL4 operating system uses a system-specific implementation of the IPC algorithms pioneered by Leidtke in developing the L4 microkernel, and later L4::Pistachio. Determining the fastest method of transmitting information between threads is very important in a microkernel environment.

Performance completely drives the design decisions, since in a microkernel environment, every IPC transfer between memory spaces requires a transition into kernel mode and back again, which requires a large number of CPU cycles. Interrupts are handled just like any other IPC. The cell which is configured to receive a given interrupt must have capabilities to this interrupt. As a result, whenever this interrupt is triggered, the kernel will send an IPC message to the thread receiving the interrupt. Requiring IPC to trigger interrupt service further drives the need for fast IPC. It is also worth noting that particular implementations of the IPC API and algorithms used by Liedtke are strongly architecture dependent. A presentation by Gernot Heiser in 2008 summarizes the actual L4 IPC performance for different architectures as shown in table 2.1.

| Architecture | Intra Address | Inter Address Space |

|--------------|---------------|---------------------|

|              | Space         |                     |

| Pentium      | 113 Cycles    | 305 Cycles          |

| AMD-64       | 125 Cycles    | 230 Cycles          |

| Itanium      | 36 Cycles     | 36 Cycles           |

| MIPS64       | 109 Cycles    | 109 Cycles          |

| ARM Xscale   | 170 cycles    | 180Cycles           |

Table 2.1: Cost of Minimal L4 IPC Transfer on Various Architectures [29]

#### 2.2.3 The SeL4 Kernel

In addition to providing fewer possible vectors for software-level attack, these second generation microkernels are small enough to go through a process of formal verification, whereby the code implemented by the operating system is proven to operate without any bugs by a set of mathematical proofs. With only a few thousand lines of code, and a minimal number of operating system hooks into user space, this verification is no longer as daunting as it would be if performed on a code base of 15 million lines of code. Researchers at National Information and Communications Technology Australia (NICTA) have developed an operating system based on L4::Pistachio called the seL4 kernel. After over seven man-years of labor, they have reportedly performed a formal verification on this microkernel, with over two hundred thousand human-and-computer generated proofs.[30]

This verification is a tremendous leap forward in creating secure and reliable computer systems. However, it is not without assumptions. One must trust the compiler, the hardware, and the proof generator. The compiler used for this verification is a derivative of the freely available GCC C-compiler, which is monolithic enough that a formal verification would be daunting, at best. Gerwin Klein has performed some initial work at NICTA in the use of a verified C compiler to compile the seL4 kernel [26], which shows promise at being a viable alternative to GCC. The seL4 kernel is designed to adhere to most ANSI C standards. This avenue is one road that could be taken to extend the research being performed at NICTA. Klein suggests that another avenue is to begin the implementation of large-scale trusted systems, such as the long-theoretical MILS architecture. [31]

As a result of this verification, secure, trusted software can be built on top of the kernel, with the separation between user-mode memory spaces abstracted as trustworthy. This makes the creation of a minimal trusted computing base (the parts of code which can bypass and compromise system security [32]) possible. Now, the formal verification of a minimalist TCB can build on the verification of the kernel itself, to create a larger secure system.

#### **2.3 A Secure Industrial System Using Microkernels**

As a result of the minimalist nature of these microkernels, and the formal verification to which they can be subjected, they can be used to create secure embedded systems. Demanding real-time requirements exist in almost all SCADA applications. IEEE and IEC standards state that many SCADA applications require a response time as low as 2-4 ms [33]. As a result, the microkernel based solution cannot be performance bound. Initial research in the implementation of a microkernel based industrial control system suggest that this is not an impossible task, with raw IPC times as low as 69.54

microseconds [1]. Additionally, the seL4 microkernel represents a basis upon which a secure separation kernel can be built, implementing with measurable certainty, a mathematically proven method for implementing such an architecture.

#### **CHAPTER III**

#### **DESIGN APPROACH**

This chapter details the design goals of the security hardened RTU prototype based on the architecture described by Hieb and Graham [1]. Many of these design goals are derived from earlier work, as described in Chapter II. While the body of work contained in Chapter II describes the security vulnerabilities in existing SCADA systems and explores the possibilities for a security hardened RTU based on microkernel operating systems, this chapter details a specific target architecture, designed with consideration for the needs of actual development, as well as the hardware available. Section 3.1 outlines the architectural model, developed by Hieb and Graham [1] of a security-hardened RTU, with respect for the possible avenues of implementation, and Section 3.2 details some of the prior work performed in creating an RTU with this architecture. Section 3.3 details how OKL4 design paradigms may be utilized for for the specified implementation, Section 3.4 details a simplified SCADA communications protocol created for testing the security features and performance of the RTU, Section 3.5 explains the operation of interprocess communication (IPC) and the communications paths through the RTU, Section 3.6 explains the usage and design of a challenge-response algorithm, and Section 3.7 describes the role based access control model utilized in this prototype.

#### **3.1 Architecture Model And Security Features**

The security hardened RTU is based on an iterative design model proposed by Hieb, Graham and Patel in a series of papers on possible security enhancements for SCADA systems. Through several papers and dissertations, this design model became increasingly specific to the architecture which could be implemented under the OKL4 operating system, as described in section 2.3.1. The model targeted at the beginning of the project was described by Hieb and Graham in [1], as shown in figure 3.1.

Figure 3.1: Target Architecture from [1]

Research performed by Graham, Hieb and Patel, among many others (See Section 2.1) has shown that the current monolithic kernel architectures contain inherent insecurities which cannot be easily mitigated through software. The above architecture, developed by Hieb and Graham is an alternative to the predominant architectures. In this new architecture, all components need not reside in the trusted computing base (TCB). The security benefits of such an architecture have been reinforced by Klein, among the primary developers of the OKL4 family of operating systems [31], in describing the use of a system very similar to this for providing security to embedded devices in a more

general sense (not just SCADA systems).

The architecture modeled in figure 3.1 visualizes the software infrastructure of a security hardened RTU. There are three isolated components: Network IO, Security, and Physical IO. This architecture decouples principal RTU functions from each other. The Network IO layer is part of the untrusted computing base (UTCB), and is a generic interface to the physical method of communicating with the RTU, whether this is industrial Ethernet, RS485, wireless data, or some other medium. This portion of the UTCB is only capable of sending inter-process communication (IPC) to the Security segment. There is no direct path of communication or memory manipulation between the Network IO and the Physical IO.

The use of a microkernel based operating system opens the possibility of creating a trusted computing base (TCB) which can be formally and rigorously verified. The security layer contains all of these necessary trusted components, including the kernel code. The security layer is capable of communicating with both the Network IO and the Physical IO. As a result, this trusted layer must mediate all communications between these two untrusted components. This layer ensures the integrity of clients across the network layer with features such as hashing and handshaking. The security module also ensures that clients posses the appropriate permissions to perform a given action, using role based access control. Although these functions are linked logically, they are, in fact, separate; hashing and handshaking verifies the integrity of the communication path, ensuring resistance against threats such as man-in-the-middle and replay attacks, while the role based access control layer ensures that the end user is performing appropriate actions (a vendor, for example, cannot change set-points, but may be able to view operations). Since the security layer is part of the trusted component of the system, it must be fast. In order to be feasibly verifiable, it must be small. The security layer must be built to facilitate later verification of functionality.

Finally, the physical IO layer consists of software which interfaces with a set of external hardware in order to generate outputs and accept inputs from the connected control system. The code to operate this subsystem is untrusted, and may only communicate with the security layer. Otherwise, the hardware and functionality of this portion is comparable to currently available and legacy commercial RTUs.

This architecture may be realized using the OKL4 operating system described in Chapter 2. As described in section 2.2.2, the OKL4 operating system makes use of memory segments, protection domains, and zones. These are combined in a logical unit called a "cell." These cells are logically separate— in fact, during the compilation process, they are compiled and linked as though they were independent programs. A utility called "Elf Weaver" combines these separate programs with the kernel code to create a bootable system image. Thus, when considered with the verification model of the OKL4 kernel describe in section 2.3.2, we can understand a cell as a realization of the kind of separation architecture described above, with the exception of two trusted "cells"— in OKL4, the kernel remains in a separate memory space and protection domain.

Each of the segments described above resides in its own cell. The physical IO resides in a cell with the remainder of the untrusted computing base. This includes utility functionality, such as hardware management, and debug interfaces. Much of this

functionality is a side-effect of creating a device which must be intricately monitored for development reasons. Security must reside in its own cell to perform trusted IPC with network and physical IO. Network IO resides in a third, separate cell. Utility functionality, such as hardware management, debug interfaces, and test code reside separate from network IO due to the complexity of the network IO code and the desire to keep possible bugs as deconvolved as possible. This design decisions simplifies development, and is otherwise arbitrary.

### **3.2 Prior Work**

This section highlights and details some sections of Chapter II which are of particular import to the development of the prototype using the OKL4 operating system, based on an architecture described by Hieb and Graham [1]. In 2007, Graham, Hieb and Patel investigated the SCADA security issues described previously, and reached a number of conclusions regarding possible directions for future research, briefly investigating the feasibility of minimizing an existing real time operating system kernel, developing enhanced SCADA protocols, and implementing role based access control on top of existing access control and security-hardening layers [34]. Hieb and Graham continued this line of research in 2008, exploring the benefits that an isolation kernel (described briefly in 2.3.2) would provide to a security enhanced SCADA system[1]. Importantly, they also performed initial experimentation using the OKL4 operating system, exploring the speed of IPC calls on real hardware. These investigations served as initial steps at developing the architecture, demonstrating that IPC overhead would not be a limiting factor in development. Hieb further described the architecture modeled above, and

continued to describe (in great detail) a role based access control system for SCADA systems, providing a framework for a role based access control system suitable for the prototype RTU considered herein [35]. A patent application has been filed for this technology. [36]

### **3.3 Isolating Components With Cells And Threads**

As mentioned above, there are two primary methods of dividing up the computing resources of a system running the OKL4 operating system – cells and threads. Threads in OKL4 are identical to threads in other operating systems. A program executed as a thread shares time on the CPU by well-understood principals of context switching. A cell, on the other hand, is a combination of many other constructs in the OKL4 Operating System. "Cell" is a glossary term, and does not actually exist as a programmatic interface in the operating system. A cell is a combination of a memory segment and protection domain, within which runs one or more threads.

A memory segment is simply an allocation of virtual memory, carved from the larger physical memory of the system. The address spaces of this virtual memory maps in a one-to-one basis with the physical memory, and must be page-aligned with the physical memory, but its addressing schema is different. A protection domain is a set of memory segments which are isolated from all other memory segments on the system. Memory segments inside a given protection domain have no way of being accessed from outside, and threads executing inside a protection domain have no access to memory segments outside their protection domain. As a general rule, memory segments cannot be mapped into more than one protection domain. Although there are exceptions to this, the

utilization of these features is not necessary for the completion of this project.

The distinction between physical and virtual memory is important. In the OKL4 operating system, all non-kernel operations exist in virtual memory space, which allows for the levels of isolation which make it possible to implement critical security components. The hardware utilities and various low-level faculties of the device are accessed using memory-mapped hardware. The configuration and data registers for these various devices reside in physical memory. This physical memory can be mapped into the virtual memory space, and the running program can discover its location at runtime without a great deal of trouble. Unfortunately, the same set of physical memory cannot be mapped in a read/write manner to two protection domains, which enforces this verified memory segment protection. As a result, there are some utility functions, such as power and clock management, which must reside in a central location. In the case of functions like these, a hardware manager thread is necessary. This hardware manager responds to requests over IPC from other cells, configuring common memory-mapped peripherals, and responds when these actions are complete. Compare this to a traditional (macro) kernel in which all driver operations have unfettered access to the entirety of physical memory.

For the purpose of debugging during development, it is necessary to create a thread with access to a common serial output. This serial output provides a way to display debug messages from multiple cells concurrently. This debug data can then be transmitted through IPC to the serial debug thread, which then utilizes the hardware of the device to generate actual output. Otherwise, the physical serial device would map to a single memory space, limiting the debug output. This becomes an issue when trying to debug IPC communications calls across multiple threads and protection domains.

Threads in OKL4 must execute within the context of a protection domain. More than one thread can exist within a protection domain, and if this is the case, each thread has unfettered access to the virtual memory mapped within that protection domain. From 3.1, a deliberate decision was made to place utility functionality separate from network functionality, in the same cell as the physical IO. This is partially due to the complexity of the network code. For the development phase of the project, it is desirable to minimize the possible source of multiply conflicting, convoluted bugs in the network code.

Threads in the OKL4 operating system can either be declared and initialized at compile time, using the elfweaver utility, or created at run-time. Creating threads at compile time is relatively simple. These threads begin at the start of execution, and continue until they terminate themselves. Capabilities, required to send IPC calls to these threads, can be declared at compile time, and assigned to other threads with which they must interact. Unfortunately, there is no built-in manner to spawn, fork, or externally terminate new threads of this type. Run time threads are better suited for applications requiring these features. Run time threads are created by another thread. This originating thread must carve out a memory space for these new threads, and must take care of their operation and termination. The major down side to this method is the creation of capabilities, which are required to communicate with the new threads. Upon starting, only the originating thread has any knowledge of the capabilities required to communicate to these threads. As a result, in order for disparate cells and threads to

communicate, the originating thread must express this capability through IPC. As the features of run time threads were not required for the construction of the target architecture, they were not used in favor of the easy of compile time threads.

In summary, for the purposes of development, there are three cells implemented in the prototype. The network IO and security cells run a single thread each, while the utility cell operates three threads-- one for network IO, one for hardware management, and one for serial debug. All threads, across all cells run at the same priority level. These threads are context switched in a round-robin fashion, without respect for their given protection domains or memory segments.

## **3.4 Inter-Cell Communication Using IPC**

All communication between components must occur through IPC, and the IPC structures in the OKL4 operating system are critical to the implementation of more complex structures, such as remote procedure call (RPC). The rules of communication must be well planned out and understood before development. Due to the complexity of initializing hardware in an operating system which provides such strong protection across memory segments, the startup sequence must be planned separate from the steady-state IPC methodologies. There is a large amount of synchrony between and among cells which must be planned for and understood in order to avoid race conditions which could cause the RTU to deadlock, either in operation or during startup.

There are two types of IPC calls in OKL4: blocking and non-blocking. Blocking calls will halt a process until the conditions for sending or receiving a given IPC are met. Non-blocking calls will attempt to deliver or receive an IPC message, and if the parter in

the communication is not ready, the attempt will fail. There are two communications primitives: send and receive. In order for a thread to send data to another thread, it must have a capability to the target thread. The capability is an object which can be passed from thread to thread, or declared at compile time. This capability is a combination of both the location of the receiving thread, as well as permissions to access this thread. The sending thread may opt to send "reply" capabilities alongside an instance of IPC. These reply capabilities are temporary capabilities to return data to the sending thread. They are invalid after the conclusion of the IPC.

These send and receive primitives combined with the ability to transmit reply capabilities can be combined in complex ways in order to achieve the security goals of the project. For the security hardened RTU, only blocking primitives are necessary. The flow of IPC through cells can be modeled as a finite state machine. Because of this, threads have no need to continue operating while they are awaiting a message,

As mentioned above, there are two "time periods" of interest for IPC. During startup, the hardware manager must enable hardware and alert cells to the initialized hardware in an order which does not halt the system. Race conditions must be avoided. During startup, the communication taking place is as shown in Figure 3.2.

Figure 3.2: IPC messages during Start-up

The hardware manager initializes hardware for serial debug, physical IO, and network IO. The hardware manager then permanently halts. Subsequently, the physical IO and Network IO communicate with the serial debug thread. All threads then enter a wait state. The serial debug may receive an IPC message from any thread, and will output this message to the terminal. Blocking "send" calls are used in order to ensure that all debug output will be seen. If a cell cannot deliver its output, it will wait until the serial debug is available. As a side-effect, however, the serial debug must be stable. Any crashes in the serial debug thread will halt the system. This ensures that testing and debugging remain consistent and simple, but provides a method for halting the system abruptly. In a production device, there would be no serial debug, so this is not a security issue. The serial debug is simply a reality of development. During steady-state, the chain of IPC events can be modeled as in Figure 3.3.

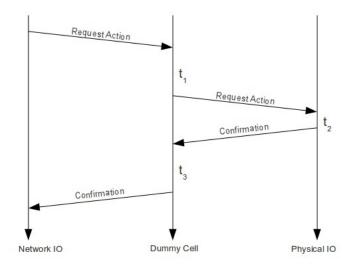

Figure 3.3: IPC from Network Event to Physical IO, given proper role based access control credentials

In figure 3.1, a message is delivered to the network cell, and relayed to the security cell. The security cell flags this as a critical point, and demands that the request be authenticated. It relays this demand to the network IO layer. A valid authentication is returned and verified by the security cell. The queued operation is then internally recalled, and its permissions are checked inside the security cell. These permissions are valid, and the security cell passes the command to the Physical IO layer, which returns some data. This data is then passed through the security layer to the network IO cell for relay to the original client.

Figure 3.4 shows a similar attempt to request some data. This time, the given RBAC credentials disallow the operation. As a result, the security cell replies to the network cell to re-enter its wait state, without sending a response. From these two examples, it's very easy to see the statefullness of the system. Figure 3.5 shows all possible states.

Figure 3.4: IPC from network event to physical IO, given improper role based access control credentials

This IPC ties the handshaking and role based security features together. All of these operations are performed in the security cell, after being received by the network cell.

Figure 3.5: Full state diagram for IPC.

## **3.5 Security Features**

The security hardened prototype will utilize several layers of security which have been implemented on devices in the past. With the ability to place these features inside a verified trusted computing base, these features become much more trustworthy. First, a simplified SCADA protocol was developed. This protocol reasonably emulates commercial SCADA protocols, allowing for easy expansion with new security features, which can then be tested for security, performance and reliability. This protocol is used internally and externally. External transit is provided by the UDP protocol. A standard handshaking authentication method is used to verify the integrity of users attempting to use the communication link, and a role base access control layer ensures that they users are permitted to perform the actions they are requesting.

### 3.5.1 A Simplified SCADA Protocol

Modern SCADA devices utilize a large number of different communications protocols over a large number of different potential communications media. The RTU prototype will communicate solely over Ethernet. In order to test the security and performance of this RTU, a full suite of SCADA functionality is unnecessary, and developmentally burdensome. Protocols like ModBus and DNP3 can very quickly become complicated, and the prototype RTU will not support the majority of these protocols' features, in any case. For development and testing, a very basic SCADA protocol is needed.

This protocol must implement the minimum number of features necessary to properly emulate a typical RTU, and remain extensible for the addition and testing of security features. SCADA operations affect control points, and control points may be either read, selected, or operated upon. Modern SCADA protocols require a select followed by an operate (with identical data payloads) in order to alter the setting of a given point. In addition to this, we must generate responses to read request, and implement our hashing and handshaking algorithm. Operate and select operations do not require a response. In order to verify the operation of an operate or select, the user performs a read operation. This write-then-read paradigm is common to many SCADA systems, and is not unique to this prototype. With this description, our simplified SCADA protocol must implement only five operations. Protocols such as ModBus and DNP3 derive their respective complexities through support for complex addressing, CRC and data integrity verifications, and standardized maps of points and operations and implementations of a variety of standardized data expression techniques.

In order to implement the role based access control mechanisms described in section 3.7, each operation must be associate to a specified user. Beyond this, the data required for an operation is dependent on the operation. A read operation requires only the point which must be acted upon. A select or an operate operation, meanwhile, requires both a point and data. Read responses include only return data, without notification of which point the read response is for. Challenge requests include a payload of a server nonce, while challenge responses include a client nonce, as well as a SHA-256 hash.

For the prototype, the payload size for user identification will be one byte, point identification will be one byte, point data will be one byte, nonces will be 4 bytes, and the SHA-256 is 32 bytes. The total size of the packet payloads, as well as operation ID is summarized in Table 3-1.

| <b>Operational Type</b> | <b>Operation ID</b> | Data     |

|-------------------------|---------------------|----------|

| Read Point              | 0x00                | 3 bytes  |

| Select Point            | 0x01                | 4 bytes  |

| Operate Point           | 0x02                | 4 bytes  |

| Demand Challenge-       | 0x03 4 bytes        |          |

| Response                |                     |          |

| Challenge-Response      | 0x04                | 36 bytes |

Table 3.1: Summary of Simplified SCADA Communications Protocol used in RTU Design

The data size indicated above includes the user and point ID bytes, but does not include the operation ID byte.

0x05

4 bytes

For reading a point, the data format is:

<Operation ID>+<User ID>+<Point ID>,

each a one-byte field.

Read Response

For select or operate operations, the format is:

<Operation ID>+<User ID>+<Point ID>+<Data>

For initial testing, Select simply operates as a "write" operation, although typical SCADA

systems require a select followed by an operate, containing identical data.

For demand-response operations, the format is:

<Operation ID>+<Server Nonce>

with the server nonce being a 4 byte field.

For challenge-response operations, the format is

<Operation ID>+<Client Nonce>+<Hash>

The client nonce is a four byte field, while the hash is a four byte field. Although the SHA-256 hash is 32 bytes in length, many commercial SCADA devices compare only the first four bytes for authentication. In this implementation, neither the client nor the server require the originating message to be hashed along with the nonce. This was excluded for simple testing and rapid development, but is a trivial addition given the current state of the code base.

For read response operations, the format is

<Operation ID>+<User ID>+<Point ID>+<Data>.

In all of the above cases, '+' indicates bit concatenation. There is no delimiter of information, other than the knowledge that each field is a strictly fixed length.

Below is an example of a "Read Response" packet, sent using user ID two, from point ID ten:

|  | 0x05 | 0x02    | 0x0A     | 0x01     |

|--|------|---------|----------|----------|

|  | Read | User ID | Point ID | Returned |

|  | Read |         |          | Data     |

This information will be wrapped in the payload of a standard UDP packet. The port 1200 is selected arbitrarily. UDP is selected due to its simplicity and ubiquity in modern Ethernet networks. A stateless UDP engine can be trivially constructed, and many, many programming languages and development environments include methods for interacting with standard UDP packets. Additionally, these UDP packets are routeable across the larger Internet.

On the RTU, the code which sends and receives these simplified SCADA packets is very simple. The decision tree for this functionality is shown in Figure 3.6.

Figure 3.6: Decision tree for SCADA packet reception.

As can be seen, there are only a handful of decisions points in the packet reception mechanism. This greatly simplifies the network layer code required. This decision tree is simplified and does not represent the role based access control decisions being made by the security layer. This diagram also does not represent the role the security cell must play in generating hashes and performing handshaking. The simple SCADA packet reception code does not need any awareness of state in order to perform its duties– it is not required to keep track of authentications, points read, or any other state. For read requests, the RTU will send a response, and allow the client to sort out which packet for which response is directed. For handshaking, the requested operation is placed on a queue, and if the client responds with valid authentication, this action is removed from the queue, and placed through the simple SCADA decision tree as though it were any other packet. Failed attempts to authenticate are simply ignored.

## 3.5.2 User Authentication And Handshaking

The method for determining the authenticity of the clients is a simple challengeresponse handshake using a pre-shared secret. This is computationally simple, and actively used in commercial SCADA devices. The only prerequisites for this method of authentication are the ability to generate random numbers, and the ability to perform a SHA-256 hash. The algorithm itself is trivially simple.

For the purpose of the prototype, it is sufficient to demonstrate that hashing can be performed, and that it is both fast and reliable. For the prototype, hashing is only performed on points which are declared "critical." If a critical point is manipulated, an authentication is demanded of the client, regardless of how recent a previous authentication may have occurred. Future implementations and expansions of this system may consider more complex methods of determining when a challenge-response handshake should occur, and include features such as caching of credentials.

If a critical point is requested, this operation is cached, and the server (RTU) demands a response from the client. This response includes a nonce generated by the server. The client receives this request, and generates its own nonce. These values are bitwise-concatenated with a pre-shared secret. A SHA-256 hash is generated on this bit

concatenation, and the hash value, along with the client nonce are returned to the server. Upon reception, the server verifies the authenticity of the hash, and if the hash is valid, pulls the operation off the queue, and executes the operation as though it were a new request. If the hash is invalid, no response is sent, and the RTU re-enters a wait state.

## 3.5.3 Role Based Access Control

The role based access control to be implemented on this RTU prototype is modeled after the access control system described in Hieb[35]. In order to facilitate prototyping, this system has been simplified from the system Hieb describes. These changes facilitated the rapid development of a system which can demonstrate the capability of a limited RTU to perform complex security operations using IPC of the sort found in the OKL4 operating system. The principal sacrifice is that of future expandability. Although the role based access control system described herein implements most of the features described by Hieb, they will not be expandable without some sacrifice in performance.

There are several object types in this role based access control system. "User" refers to the credentials passed to the RTU and "Points" represent the physical IO to be manipulated or read. Users maintain membership to one or more roles, and these roles have access to one or more sets of permissions. A permission is a set consisting of a point combined with point access controls. A point is a physical IO (or abstraction of physical IO) whose state may be altered, while a permission represents the actions that may be performed on the IO. In the target implementation, permissions may be read-only access or full-access.

Points have associated point types, which are labels used to more broadly control permissions. Roles have, in addition to associated permissions, point type controls, which govern whether or not a role may have access to a given point type regardless of permission. Roles further have point access constraints, which are further restrictions on how a role may access a given point. In the target implementation, only time-of-day and day-of-week point access constraints are considered, while Hieb describes further restrictions, such as terminal location, among others.

Users have a similar constraint in the form of role access constraints. Users may have restrictions placed on how they may use a particular role to which they are assigned. The goal targeted only temporal restrictions, while Hieb further expands on the possible implementations of such restrictions. Permissions in this manner are assigned in a logical OR fashion: If any of the set of permissions assigned to a user allow an action, this action is allowed to occur. If the action is not allowed to occur, the client is not notified of this failure. Only later reinspection will inform the user that their access permissions have been denied.

In order to simplify development, roles, users, points and all other controls relating to the RBAC feature are hard-coded into the system, and cannot be modified at run-time. Any access constraints which depend on information other than time of day have not been designed into this system. In order to check permissions and easily iterate through sets of permissions, users, and points, many access controls are stored as bitfields. This allows the use of native bitwise logic operations in order to determine positions. Since these permissions are permissive by default, their inspection is simple.

# **3.6 Design Summary**

The security hardened prototype architecture makes use of several security features available with a microkernel like OKL4, which provides the ability the separate thread and memory spaces. Figure 3.1 provides a high level overview of this architecture, which will be implemented in the OKL4 operating system using thread and cells as units of separation between the zones defined in this figure. These cells will consist of a network IO cell, a security cell, and a physical IO cell. The physical IO cell will also include all utility functionality which is local to the RTU prototype, including debug outputs and hardware management. This is the bulk of the untrusted computing base. The security cell contains the entirety of the trusted computing base, with the exception of the operating system kernel. This kernel is abstracted from user-mode access, but for architectural purposes can be visualized as a separate cell running a separate thread. The remainder of the untrusted computing base lies in the network communication cell. Although this code is in the UTCB just as the physical IO, the network and physical IO reside in different memory spaces. The only method of transferring information and messages from physical IO to network IO (and vice versa) is through the security cell. This is where the verifiable security of the prototype RTU is defined. Chapter IV will continue to detail the implementation of the features described above.

#### **CHAPTER IV**

## **IMPLEMENTATION**

This chapter describes the implementation of the design described in Chapter III. This will include an overview of the hardware selected, and the OKL4 development environment in Section 4.1, a description of the IO hardware and software in Section 4.2, and the necessary implementation of some utility functions in Section 4.3. Network hardware and software is discussed in Section 4.4, and finally, security software descriptions are located in Section 4.5. These subsections will briefly review the architectural choices from Chapter III, then discuss the actual implementation, along with any necessary architectural changes.

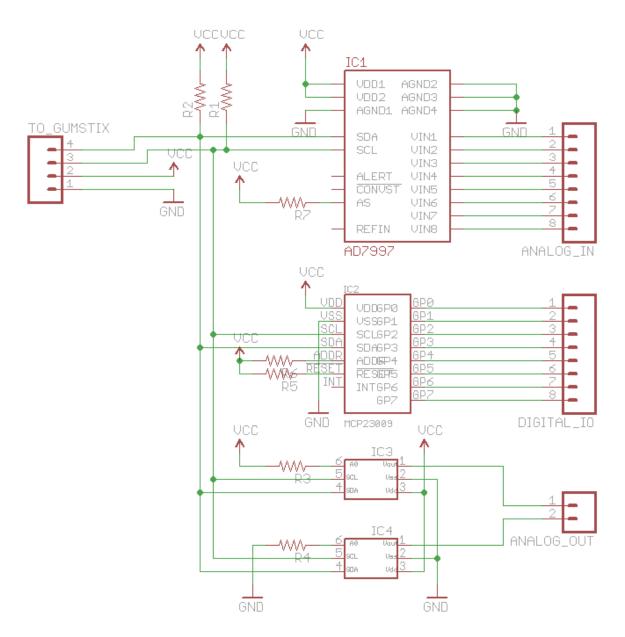

### 4.1 Hardware, Build System, And Workflow

The primary hardware platform for this project is the Gumstix Verdex Pro XM4 COM board. The Gumstix platform is a simple, embedded computer module which includes an Intel Xscale PXA microprocessor, 64 megabytes of RAM, and 16 megabytes of flash memory. The module also includes expansion connectors which are used general purpose IO (GPIO) and network connectivity. This module includes a PXA270 chip clocked at 400MHz. The PXA270 is a 32-bit microcontroller based on the ARMv5 architecture. Although dated (from 2007), the processor compares favorably to existing RTU devices. Datasheets and application manuals are commonly available from Marvell and Intel [37].

The Gumstix Platform was selected for its expandability and compatibility with

available OKL4 Distributions, as well as its similarity to existing RTU hardware. The OKL4 microkernel is currently targeted towards the cell phone and mobile device market. Although the PXA270 was designed principally as a mobile device chip, its specifications are not dissimilar from RTUs already on the market. This chip is compatible with both Linux and the OKL4 Development Environment, allowing for testing in a real-world environment.

Along with the Gumstix, the console-VX and netpro-VX expansion boards are used. The console-VX provides pin headers for all three universal asynchronous receiver/transmitters (UART) on the PXA270 Chip, as well as pin-headers for Audio, inter-IC Bus (I2C), and several GPIOs. The netpro-VX includes an SMC9118 network PHY/MAC interface for network connectivity.

In order to boot the Gumstix board, a bootloader (Uboot) resides in flash memory. The remainder of flash is utilized by the JFFS2 file system. This file system is designed for flash storage, and in the gumstix environment, is pre-loaded with a Linux distribution. Uboot executes a startup script, which loads a program image from flash, microSD, or over the network into RAM, and then begins execution at that location. RAM begins at memory address 0xA2000000 and ends at address 0xA3F00000. In order to properly boot the Gumstix board, an image must be loaded into memory in either ARM ELF or Intel Hex format. The factory default bootloader script has been modified for this project to load an image over the network, via TFTP, load it into RAM, and execute.

The OKL4 operating system used for this prototype is version 3.0. The verified kernel which branches from the OKL4 project is based on version 3.0 of the operating

system. The operating system is provided as a precompiled ELF file. The devleopment kit includes a C and C++ compiler chain based on GCC. This GCC compiler is modified to cross-compile for the ARM chip on the Gumstix board, and the SDK includes Make files which abstract the inclusion of OKL4 Libraries and ElfWeaver calls. GCC and its linker produce output ELF files individually for each cell in the source tree structure. Each cell has associated XML files which define characteristics such as default priority, heap and stack sizes, and capabilities. There are further XML files which describe the structure of a complete project, and still more XML files which define the hardware available on the development platform. These XML files are used after the compilation process by the ElfWeaver tool.

The operation of the compiler and linker are unremarkable. The OKL4 libraries included make use of basic kernel structures and system calls, and may be compiled into each cell independent of the kernel code. Each cell is compiled as its own individual program. Thus, the compilation tools and methods are independent of the OKL4 operating system. It is the ElfWeaver tool which manipulates these compiled ELF files in order to create a working OKL4 system. Elfweaver uses the XML files in order to determine the manner in which the resulting ELF files must be linked to the kernel. This linking takes place in an inside-out order. First, the compiled output files from GCC and its linker are combined with the per-cell XML file, relocating the memory space of the program, and making note of required cell characteristics such as capabilities, threads, memory sections, and other attributes.

Next, the cells are linked to the kernel, with the kernel getting assigned memory sections