# University of Louisville

# ThinkIR: The University of Louisville's Institutional Repository

**Electronic Theses and Dissertations**

5-2014

# Low power strain sensor based on MOS tunneling current.

Li Zhu University of Louisville

Follow this and additional works at: https://ir.library.louisville.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Zhu, Li, "Low power strain sensor based on MOS tunneling current." (2014). Electronic Theses and Dissertations. Paper 1648.

https://doi.org/10.18297/etd/1648

This Doctoral Dissertation is brought to you for free and open access by ThinkIR: The University of Louisville's Institutional Repository. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of ThinkIR: The University of Louisville's Institutional Repository. This title appears here courtesy of the author, who has retained all other copyrights. For more information, please contact thinkir@louisville.edu.

## LOW POWER STRAIN SENSOR BASED ON MOS TUNNELING CURRENT

Ву

## Li Zhu

B.S., Beijing Institute of Technology, China, 2007

M.S., Beijing Institute of Technology, China, 2009

## A Dissertation

Submitted to the Faculty of the

J. B. Speed School of Engineering of the University of Louisville

in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

University of Louisville

May 2014

# Copyright 2014 by Li Zhu All rights reserved

# LOW POWER STRAIN SENSOR BASED ON MOS TUNNELING CURRENT

Ву

# Li Zhu

B.S., Beijing Institute of Technology, China, 2007

M.S., Beijing Institute of Technology, China, 2009

# A Dissertation Approved on April 21, 2014

| by the following Dissertation Committee: |

|------------------------------------------|

| Shamus McNamara, Ph.D                    |

| Kevin Walsh, Ph.D                        |

| John Naber, Ph.D                         |

| Sergio Mendes, Ph.D                      |

| Gamini Sumanasekera Ph D                 |

# **DEDICATION**

This dissertation is dedicated to my family, especially to my parents, Xingqi Zhu and Hongmei Zhang, who guide me and support me for over 20 years;

to my wife, Mingxia, for being a great wife; to my new born lovely boy, Yicheng, for his cheerful smile.

#### **ACKNOWLEDGMENTS**

I would like to give my deepest appreciation to my advisor Dr. Shamus McNamara. He has demonstrated himself as a great mentor in both research and daily life. He never hesitates to give his help and guidance whenever I have questions about experiment, documentation and presentation. He is serious about everything he works on. In the same time, he always smiles when I speak with him, which is really cheerful and warm.

I also would like to thank my committee members, Dr. Kevin Walsh, Dr. John Naber, Dr. Sergio Mendes and Dr. Gamini Sumanasekera. They have been very helpful on my research. Dr. Kevin Walsh and Dr. John Naber have given me a lot useful suggestions on my research and have been very generous to let me use instruments in their labs. Dr. Sergio Mendes and Dr. Gamini Sumanasekera gave me a lot helpful ideas during my dissertation proposal and research.

I want to thank my previous and current lab colleges, Dr. Chakravarthy Yamarthy, Dr. Kunal Pharas, Alexander Bell, Stephanie Miles, Abderrazzak Faiz, Mark Crain, Pranoy Shuvra and Bryan Snatchko. Especially thanks to Dr. Kunal Pharas. He is a great friend. I still remember that he showed me around the campus of University of Louisville when I first came to the university. He was very patient when he was my cleanroom "buddy". He shares a lot of ideas in both research and life with me. Mr. Mark Crain has been very helpful with suggestions on micro-fabrication. I also thank Douglas Jackson and Thomas Roussel. Doug has helped me a lot in circuit design and experiments.

I am really impressed by his fancy tools and gadgets. He is a very experienced engineer, and he always has an answer to my questions. Thomas is definitely an expert in software and programming. He has done a great job in set up and maintaining the KRUNCH server. His experience in MEMS modeling and Labview was really a great help to me.

I also appreciate staff in Micro/Nano Technology Center. Without their hard work to maintain cleanroom instruments, I would never be able to make any devices and do my research.

I also would like to thank my dear friends in Louisville, Dr. Huihang Dong, Dr. Dongqing Chen, Dr. Hui Wang, Dr. Xinghua Sun, Dr. Mingxiao Li, Shuangshuang Jiang, Hanwen Yuan, Jason Li, etc. It is my great honor to have them as my friends. Their friendship and encouragement keep me positive during my research and daily life.

Last, I want to give most thanks to my family, especially my wife, Mingxia Liu, my son, Yicheng, my parents and in-laws. Mingxia is not only a great wife, but a heart-to-heart friend. She always takes care of my daily life, reminds me of every important thing, encourages me and gives me her love. I also want to thank her for giving birth to our lovely angel, Yicheng, who is now our family's biggest source of happiness.

#### **ABSTRACT**

#### LOW POWER STRAIN SENSOR BASED ON MOS TUNNELING CURRENT

#### Li Zhu

## April 12, 2014

Sensors, such as pressure sensors, accelerometers and gyroscopes, are very important components in modern portable electronics. A limited source of power in portable electronics is motivating research on new low power sensors. Piezoresistive and capacitive sensing technologies are the most commonly utilized technologies, which typically consume power in the µW to mW range. Tunneling current sensing is attractive for low power applications because the typical tunneling current is in the nA range.

This dissertation demonstrates a low power strain sensor based on the tunneling current in a metal-oxide-semiconductor (MOS) structure with a power consumption of a couple of nano-Watts (nW) with a minimum detectable strain of 0.00036%. Both DC and AC measurements were used to characterize the MOS tunneling current strain sensor. The noise level is found to be smallest in the inversion region, and therefore it is best to bias the device in the inversion region.

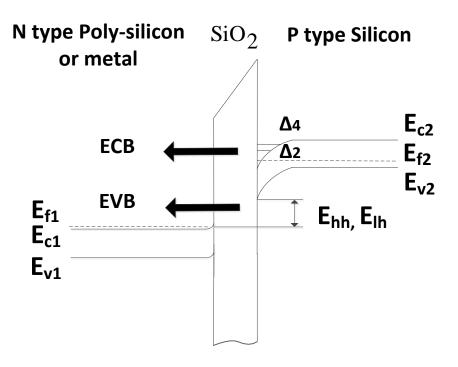

To study the sensitivity in the inversion region, a model is developed to compute the tunneling current as a function of strain in the semiconductor. The model calculates the tunneling current due to electrons tunneling from the

conduction band of the semiconductor to the gate (ECB tunneling current) and the tunneling current due to electrons tunneling from the valence band of the semiconductor to the gate (EVB tunneling current). It is found that the ECB tunneling current is sufficient to explain experimental gate leakage current results reported in the literature for MOSFETs with low substrate doping concentration. However, for the tunneling current strain sensor with a higher substrate doping concentration reported here, a model using both ECB and EVB tunneling current is required. The model fits our experiments.

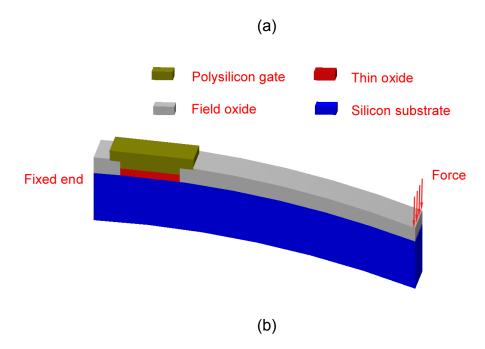

During both DC and AC measurements, the MOS tunneling current is found to drift with time. The drift could arise from the trap states within the oxide. The current drift makes it difficult to obtain an absolute measurement of the strain. Combining the tunneling current strain sensor with a resonant sensor may be a good choice because it measures changes in the mechanical resonant frequency, independent of a drift of the tunneling current amplitude.

# TABLE OF CONTENTS

| DEDI | CATION   |                                                          | iii  |

|------|----------|----------------------------------------------------------|------|

| ACKI | NOWLED   | OGMENTS                                                  | iv   |

| ABST | RACT     |                                                          | vi   |

| LIST | OF TAB   | LES                                                      | xii  |

| LIST | OF FIGL  | JRES                                                     | xiii |

| CHAF | PTER 1   | INTRODUCTION                                             | 1    |

| 1.1  | Motivat  | ion                                                      | 1    |

| 1.2  | Releva   | nce of the research                                      | 5    |

| 1.3  | Outline  | of Dissertation                                          | 6    |

| CHAF | PTER 2   | INTRODUCTION TO MOS TUNNELING CURRENT                    | 9    |

| 2.1  | History  | of quantum tunneling studying                            | 9    |

| 2.2  | Differe  | nt Types of Tunneling current in MOS capacitor           | 12   |

| 2.3  | Derivat  | ion of Fowler-Nordheim tunneling current equation in MOS |      |

|      | structu  | re                                                       | 15   |

|      | 2.3.1    | Tsu and Esaki model for Fowler-Nordheim tunneling curren | nt   |

|      |          | equation                                                 | 16   |

|      | 2.3.2    | The WKB method                                           | 19   |

| 2.4  | Direct t | unneling in MOS structure                                | 26   |

|      | 2.4.1    | Derivation of the direct tunneling formula               | 27   |

| 2.5  | Summa    | ary                                                      | 29   |

| CHAF | PTER 3   | STRAIN EFFECTS IN SILICON                                | 31   |

| 3.1  | Silicon band structure 3 |                                                   |    |  |

|------|--------------------------|---------------------------------------------------|----|--|

| 3.2  | Stress                   | Stress tensor 3                                   |    |  |

| 3.3  | Strain t                 | Strain tensor 39                                  |    |  |

| 3.4  | Strain e                 | effects on silicon band structure                 | 37 |  |

| 3.5  | Summa                    | ary                                               | 42 |  |

| CHAF | PTER 4                   | EXPERIMENTS ON MOS TUNNELING CURRENT              | 43 |  |

| 4.1  | Introdu                  | ction                                             | 43 |  |

| 4.2  | Fabrica                  | ation and Measurement setup                       | 45 |  |

| 4.3  | DC exp                   | periments of strain effects on tunneling current  | 49 |  |

|      | 4.3.1                    | Tensile strain                                    | 50 |  |

|      | 4.3.2                    | Compressive strain                                | 54 |  |

|      | 4.3.3                    | Discussion                                        | 57 |  |

| 4.4  | AC exp                   | eriments of strain effects on tunneling current   | 58 |  |

|      | 4.4.1                    | The principle of AC measurement                   | 58 |  |

|      | 4.4.2                    | Results and discussion                            | 61 |  |

|      | 4.4.3                    | Conclusions                                       | 67 |  |

| CHAF | PTER 5                   | MOS STRAIN SENSOR SENSITIVITY STUDY BASED O       | N  |  |

|      |                          | ECB AND EVB MODELING                              | 69 |  |

| 5.1  | Introdu                  | ction                                             | 69 |  |

| 5.2  | ECB m                    | odeling                                           | 70 |  |

|      | 5.2.1                    | Approximate methods for quantized inversion layer | 72 |  |

|      | 5.2.2                    | ECB tunneling current using WKB approximation     | 76 |  |

|      | 5.2.3                    | Strain induced ECB tunneling current changing     | 78 |  |

|      | 5.2.4                    | Summary of ECB tunneling current modeling         | 81 |  |

| 5.3 | EVB m    | odeling                                                    | 81    |

|-----|----------|------------------------------------------------------------|-------|

| 5.4 | ECB ar   | nd EVB tunneling current modeling for the MOS tunneling    |       |

|     | current  | strain sensor used in the DC measurement                   | 84    |

| 5.5 | Differer | nt doping concentration                                    | 88    |

| 5.6 | Summa    | ary                                                        | 92    |

| CHA | PTER 6   | BULK ACOUSTIC LONGITUDINAL RF RESONATOR                    |       |

|     |          | BASED ON MOS TUNNELING CURRENT STRAIN SEN                  | ISOR  |

|     |          |                                                            | 94    |

| 6.1 | Introdu  | ction to RF MEMS resonator                                 | 94    |

| 6.2 | Bulk Ad  | coustic RF resonator based on MOS tunneling current strair | 1     |

|     | sensor   |                                                            | 96    |

|     | 6.2.1    | Principle of bulk acoustic RF resonator                    | 97    |

|     | 6.2.2    | Fabrication of Bulk Acoustic RF resonator based on MOS     |       |

|     |          | tunneling current strain sensor                            | 98    |

|     | 6.2.3    | Bulk acoustic RF resonator testing                         | 108   |

|     | 6.2.4    | Testing and discussion                                     | 111   |

| 6.3 | Sugges   | stions for improvement in future                           | 115   |

| CHA | PTER 7   | CONCLUSIONS AND FUTURE DIRECTIONS                          | 116   |

| 7.1 | Conclu   | sions                                                      | 116   |

| 7.2 | Future   | directions                                                 | 118   |

|     | 7.2.1    | Sensitivity study at different stresses                    | 118   |

|     | 7.2.2    | Continuing research on RF resonator based on MOS tunn      | eling |

|     |          | current strain sensor                                      | 119   |

| 7.3 | Bolome   | eter based on MOS tunneling current                        | 120   |

| REE | RENCE    | 9                                                          | 122   |

# LIST OF TABLES

| Table 1  | Summaries of advantages and disadvantages for different    |     |

|----------|------------------------------------------------------------|-----|

|          | sensing methods                                            | . 4 |

| Table 2  | Summaries of gauge factor, linearity and power consumption | n   |

|          | for different sensing methods                              | . 4 |

| Table 3  | Uniformity measurement result                              | 47  |

| Table 4  | Analysis of experiment data                                | 50  |

| Table 5  | Noise measurement at different frequencies                 | 62  |

| Table 6  | Noise measurement at different time constant               | 64  |

| Table 7  | Values of effective masses used in this paper.             | 75  |

| Table 8  | Sensitivity vs. gate voltage from our group's experiment   | 84  |

| Table 9  | Summary of vibrating shapes                                | 96  |

| Table 10 | Parameters of the resonator1                               | 04  |

| Table 11 | Definition of components used in equivalent circuit 1      | 05  |

| Table 12 | Measurement results for substrate impedance 1              | 13  |

| Table 13 | Experiment result                                          | 21  |

# LIST OF FIGURES

| Figure 2.1 | FN tunneling (Figure is from [32]).                         | 10     |

|------------|-------------------------------------------------------------|--------|

| Figure 2.2 | Current-Voltage relation of a tunneling diode [32]          | 11     |

| Figure 2.3 | Band diagram of a tunneling diode at varies biases [32]     | 12     |

| Figure 2.4 | Illustration of direct tunneling in MOS structure. (a) posi | tive   |

|            | bias; (b) negative bias                                     | 14     |

| Figure 2.5 | Schematic illustrating the Trap-assist-Tunneling current    | t. The |

|            | figure is from [42].                                        | 15     |

| Figure 2.6 | Schematic illustrating Fowler-Nordheim Tunneling curre      | ent.   |

|            | The figure is from [42].                                    | 16     |

| Figure 2.7 | Schematic Illustrating for the WKB method                   | 20     |

| Figure 2.8 | Transfer matrix method [46]                                 | 28     |

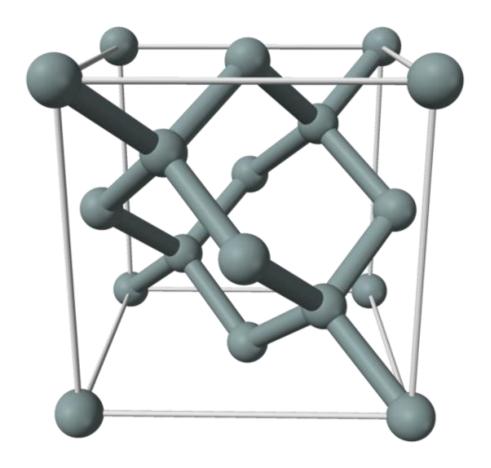

| Figure 3.1 | FCC lattice [48].                                           | 32     |

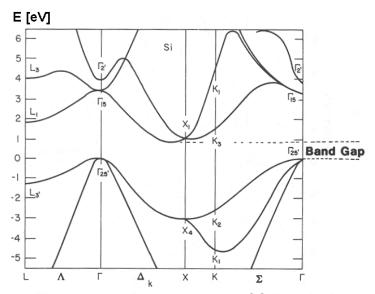

| Figure 3.2 | Band structure of Silicon [50]                              | 33     |

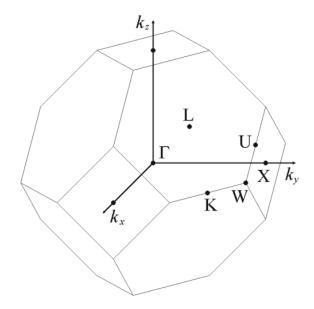

| Figure 3.3 | The first Brillouin zone of Silicon [51].                   | 33     |

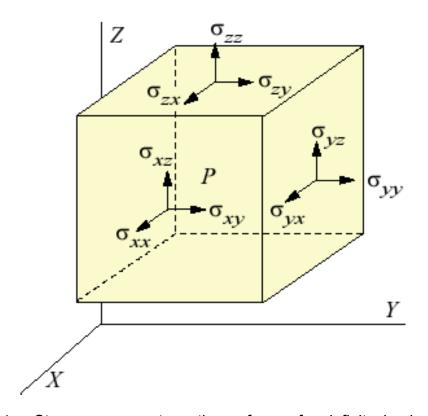

| Figure 3.4 | Stress components on the surfaces of an infinitesimal of    | ube    |

|            | [52]                                                        | 34     |

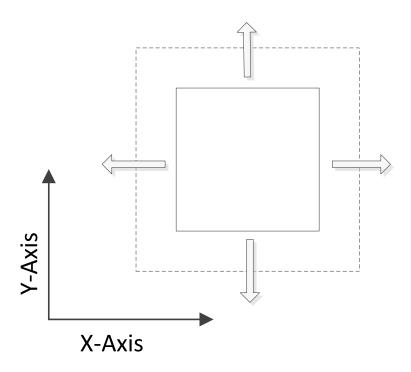

| Figure 3.5 | Biaxial stress                                              | 38     |

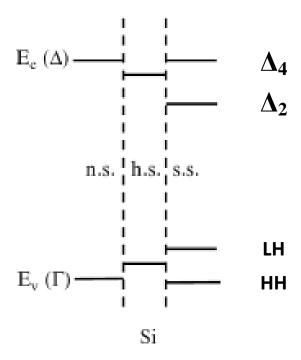

| Figure 3.6 | Band splitting of Si under biaxial tensile stress [53]      | 39     |

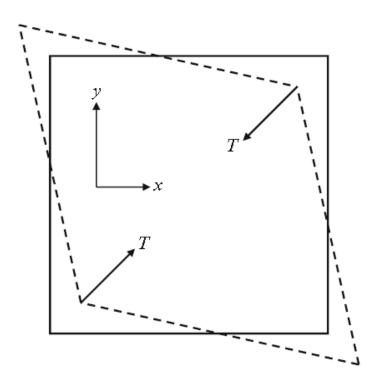

| Figure 3.7 | Uniaxial <110> stress [53]                                  | 40     |

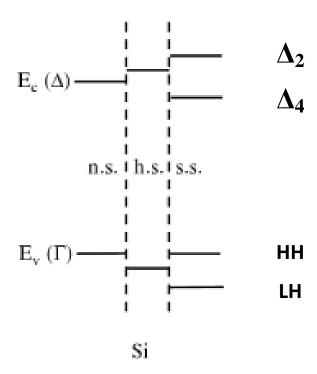

| Figure 3.8 | Band splitting of Si under uniaxial <110> compressive s     | stress |

|            | [53]                                                        | 41     |

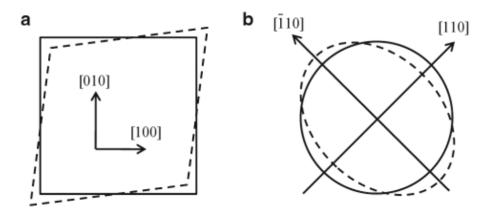

| Figure 3.9  | Uniaxial stress on constant energy surface. (a) Deformation    |

|-------------|----------------------------------------------------------------|

|             | under uniaxial <110> stress. (b) Constant energy contour in    |

|             | (001) plane [53]42                                             |

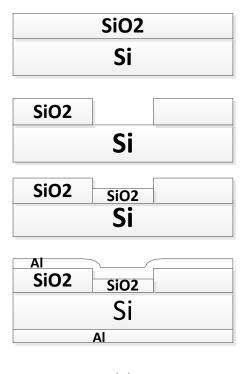

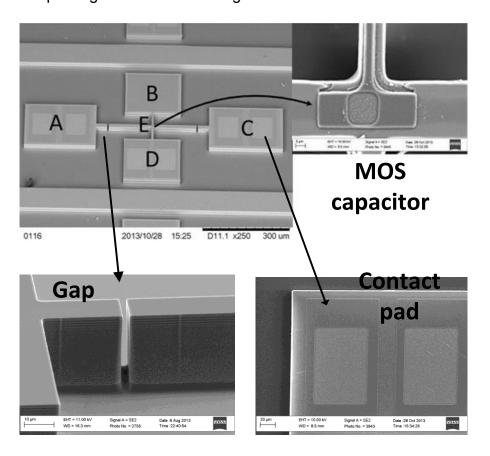

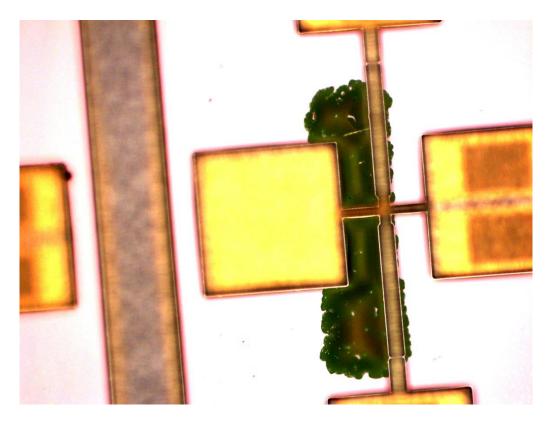

| Figure 4.1  | Fabrication process and the figure of MOS tunneling current    |

|             | strain sensor. (a). Fabrication process; (b). Picture of the   |

|             | device46                                                       |

| Figure 4.2  | P type wafer for uniformity measurement using ellipsometer.    |

|             | 47                                                             |

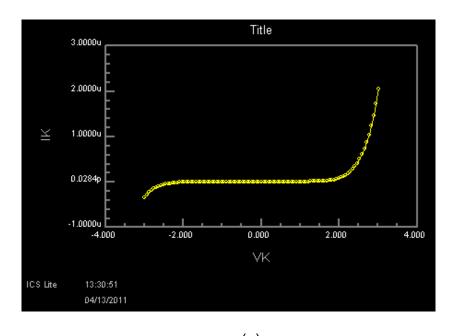

| Figure 4.3  | IV curve for MOS capacitor. (a). Good device; (b). Bad device. |

|             | 48                                                             |

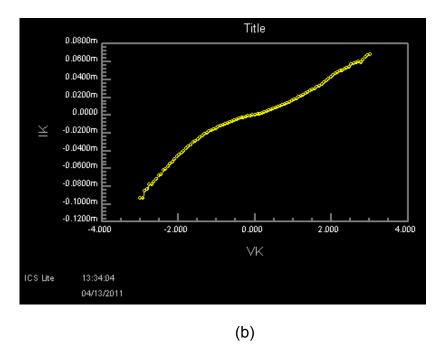

| Figure 4.4  | Photograph of measurement setup, and illustration of MOS       |

|             | tunneling current strain sensor using cantilever beam. The     |

|             | MOS device is near the fixed end. (a). Measurement setup;      |

|             | (b). Illustration of MOS tunneling current strain sensor using |

|             | cantilever beam49                                              |

| Figure 4.5  | Tunneling current versus time at different gate voltages and   |

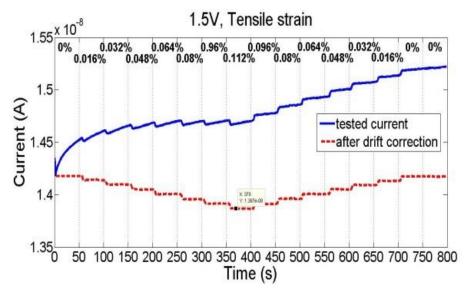

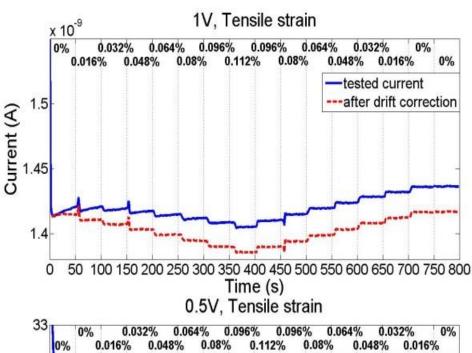

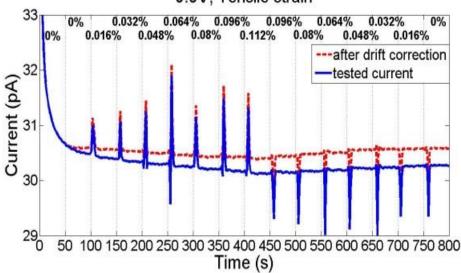

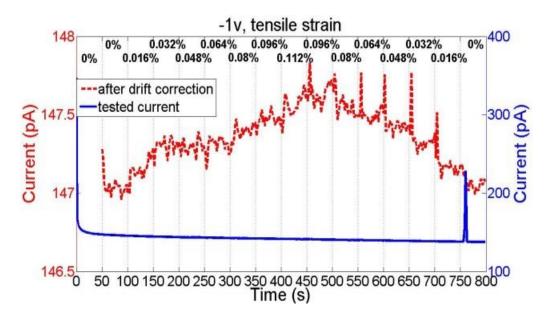

|             | different tensile strain53                                     |

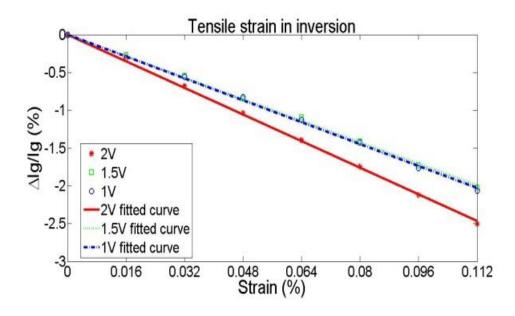

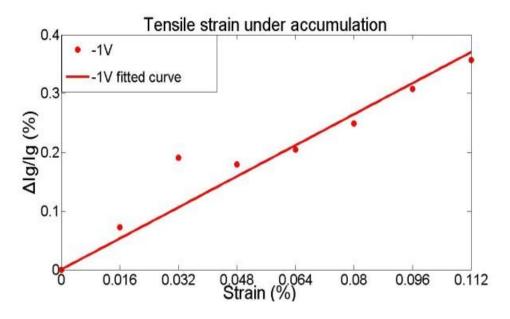

| Figure 4.6  | Tunneling current change versus tensile strain54               |

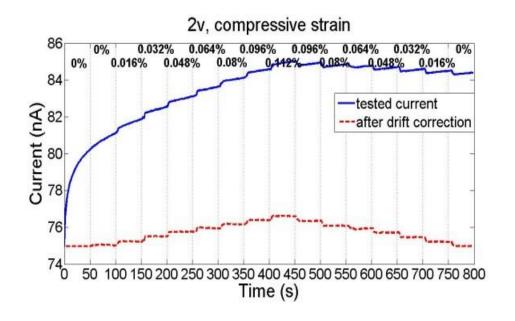

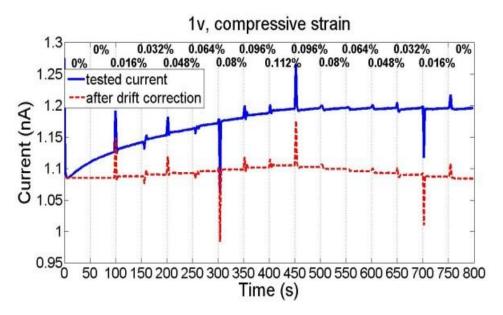

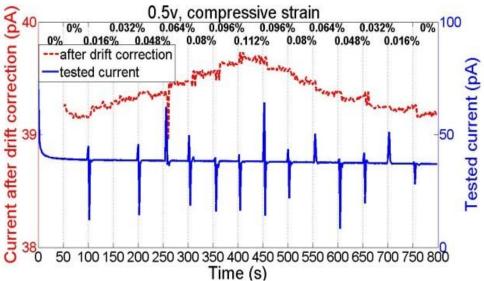

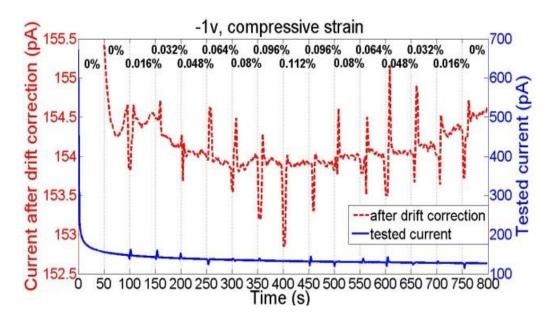

| Figure 4.7  | Tunneling current versus time at compressive strain 56         |

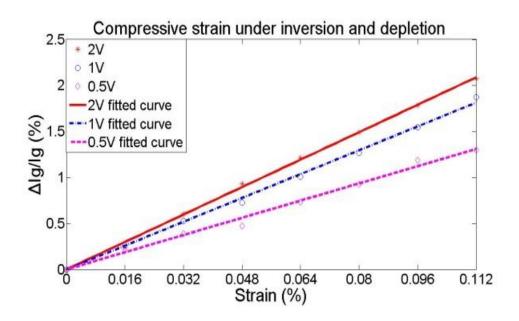

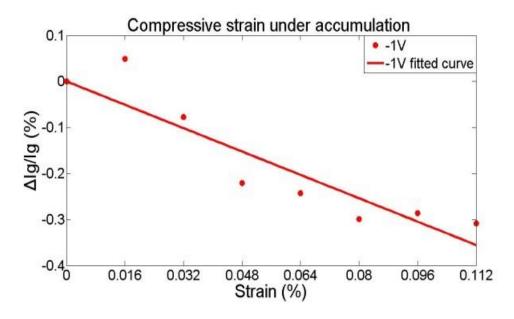

| Figure 4.8  | Tunneling current change versus compressive strain 57          |

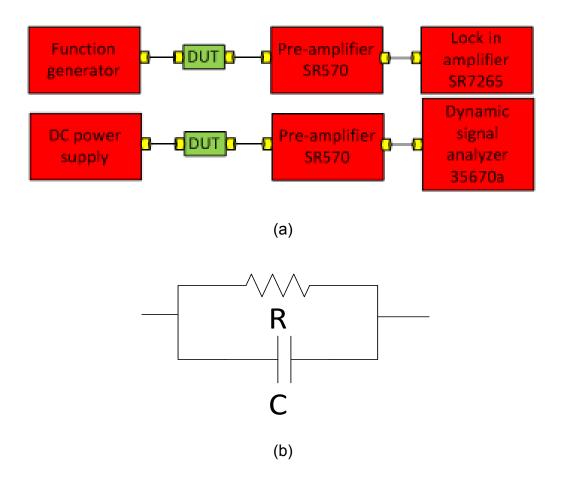

| Figure 4.9  | (a) The top one is the setup for strain measurement and the    |

|             | bottom one is the setup for noise spectrum measurement. (b)    |

|             | The equivalent circuit for a MOS tunneling sensor 59           |

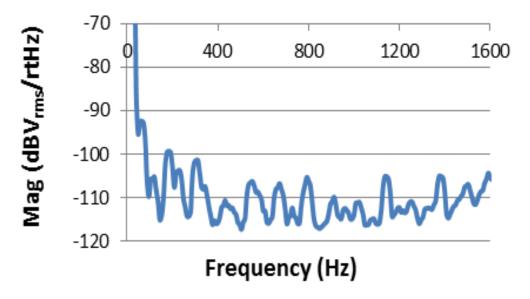

| Figure 4.10 | Noise spectrum61                                               |

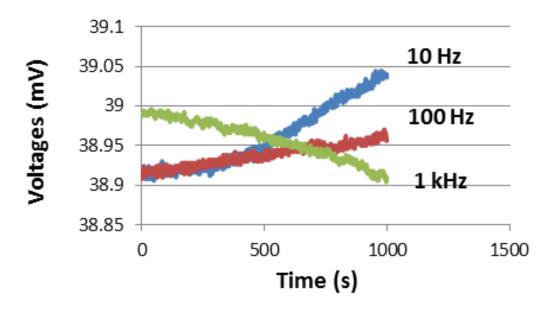

| Figure 4.11 | AC measurement at different frequencies when the time                               |

|-------------|-------------------------------------------------------------------------------------|

|             | constant is 100 ms 62                                                               |

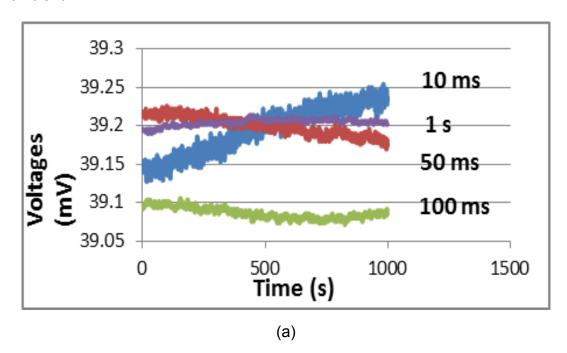

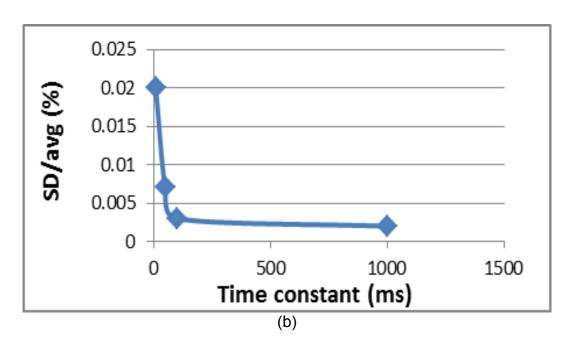

| Figure 4.12 | (a) AC measurement of different time constant at 1 kHz; (b)                         |

|             | SD/avg vs. time constant64                                                          |

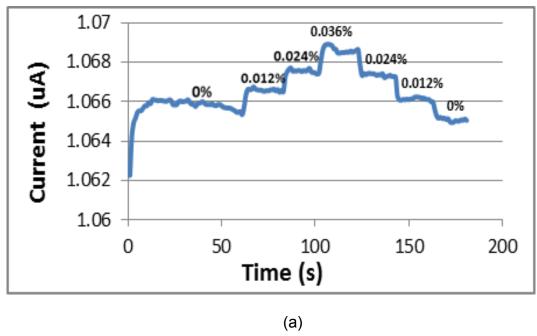

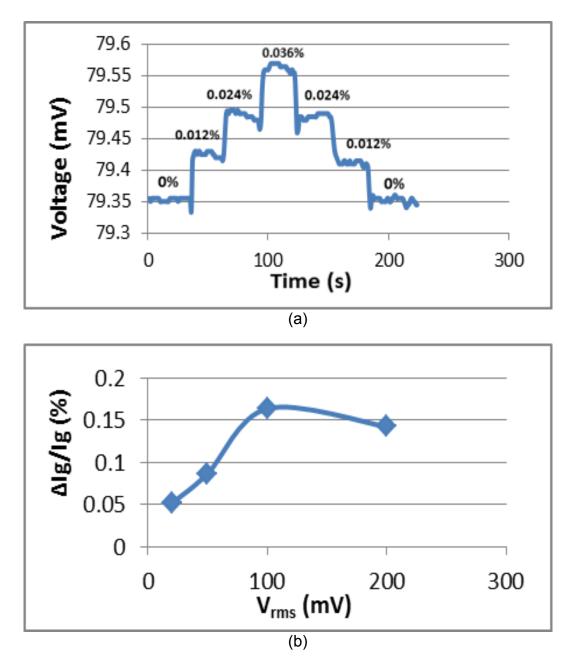

| Figure 4.13 | DC method. (a) tunneling current at $V_{dc}$ =0.7 V; (b) strain                     |

|             | response at different DC voltages at the strain of 0.012%66                         |

| Figure 4.14 | AC method. (a) tunneling current at Vrms= 100 mV, Vdc=0.7                           |

|             | V and 1 kHz; (b) strain response at different DC voltages at                        |

|             | the strain of 0.012%67                                                              |

| Figure 5.1  | NMOS in inversion region71                                                          |

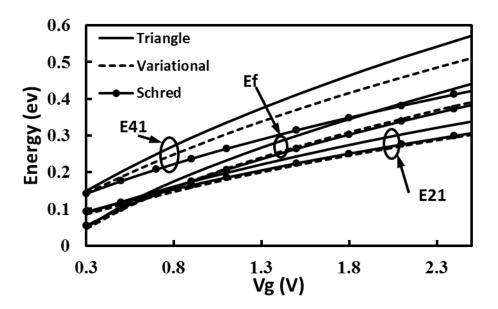

| Figure 5.2  | Sub-bands vs. gate voltage. The doping concentration of p-                          |

|             | type substrate is 1e17 cm <sup>-3</sup> . The doping concentration of n-            |

|             | type poly gate is 1e20 cm <sup>-3</sup> . The thickness of gate oxide is            |

|             | 2.19 nm                                                                             |

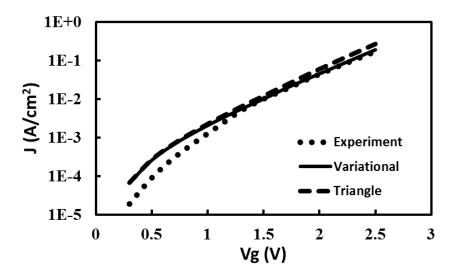

| Figure 5.3  | Gate current density vs. gate voltage. The device parameters                        |

|             | are the same as used in Figure 5.2. The experiment results                          |

|             | are from [66]78                                                                     |

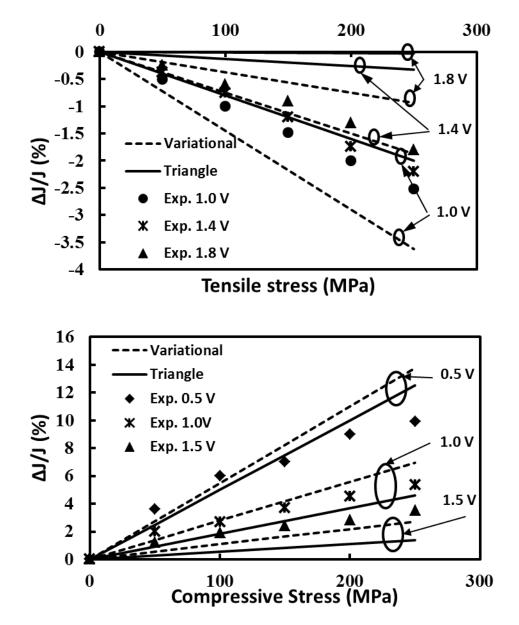

| Figure 5.4  | Modeling vs. experimental results. For the tensile case, the                        |

|             | doping concentration is 5e17 cm <sup>-3</sup> for the p-type substrate              |

|             | and 1e20 cm <sup>-3</sup> for the n-type poly gate. The thickness of gate           |

|             | oxide is 1.3 nm. The experimental data for the tensile is from                      |

|             | [56]. For the compressive case, the doping concentration is                         |

|             | 1e17 cm <sup>-3</sup> for the p-type substrate and 1e20 cm <sup>-3</sup> for the n- |

|             | type poly gate. The thickness of gate oxide is 1.3 nm. The                          |

|             | experimental data for the tensile is from [67]79                                    |

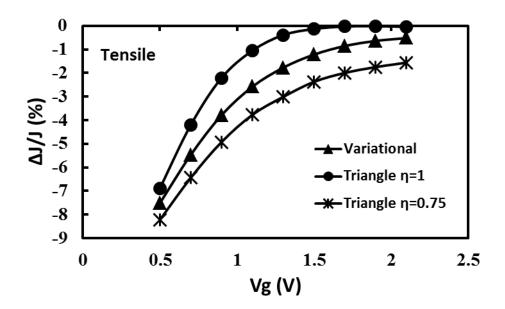

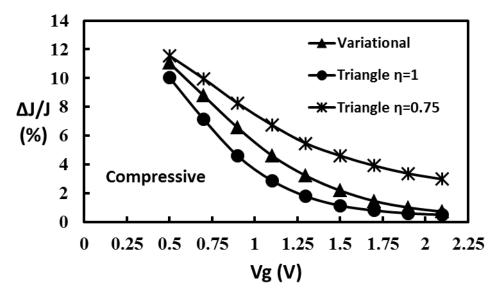

| Figure 5.5  | Percent change in current density versus voltage. The tensile      |

|-------------|--------------------------------------------------------------------|

|             | and compressive stress are both 200 MPa. The parameters            |

|             | are the same as Figure 5.481                                       |

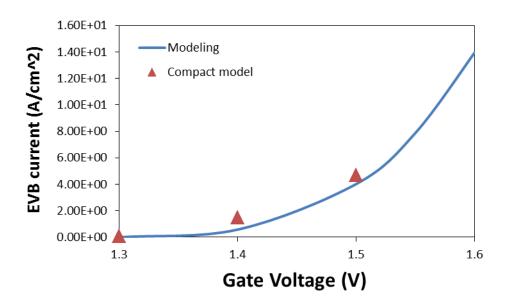

| Figure 5.6  | EVB modeling. The parameters used in EVB modeling are the          |

|             | same as those in Fig. 2 in [71]                                    |

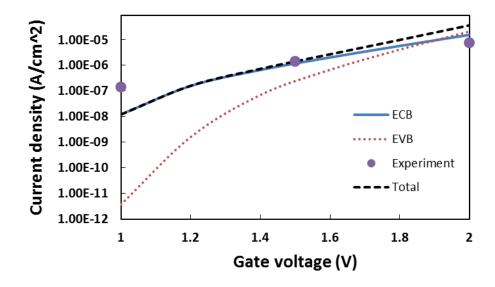

| Figure 5.7  | Calculated current density for the MOS strain sensor without       |

|             | strain, including the ECB tunneling current, EVB tunneling         |

|             | current, and the total tunneling current. A comparison to the      |

|             | experimental results are also shown85                              |

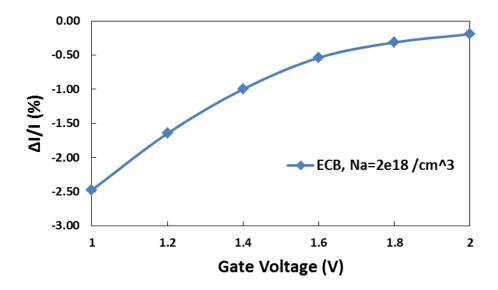

| Figure 5.8  | Sensitivity vs. gate voltage for ECB 86                            |

| Figure 5.9  | Calculated sensitivity vs. gate voltage for EVB tunneling          |

|             | current87                                                          |

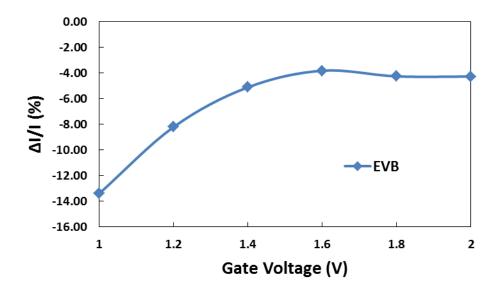

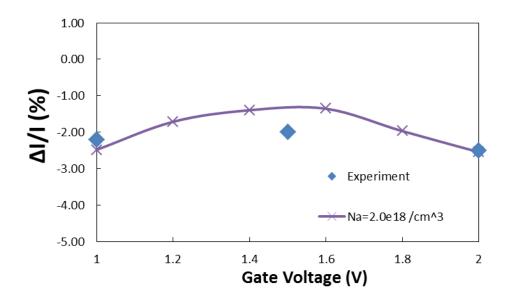

| Figure 5.10 | Sensitivity vs. gate voltage for total tunneling current. The line |

|             | is calculated from the model, and the diamonds are the             |

|             | measured experimental results88                                    |

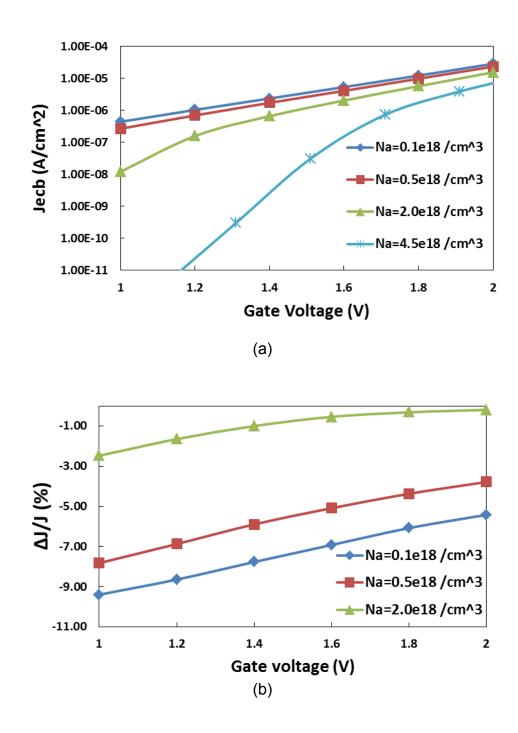

| Figure 5.11 | ECB modeling for different doping concentration. Parameters        |

|             | are the same as MOS tunneling current strain sensor in DC          |

|             | measurement. (a). Current density vs. gate voltage for ECB;        |

|             | (b). Sensitivity vs. gate current for ECB 89                       |

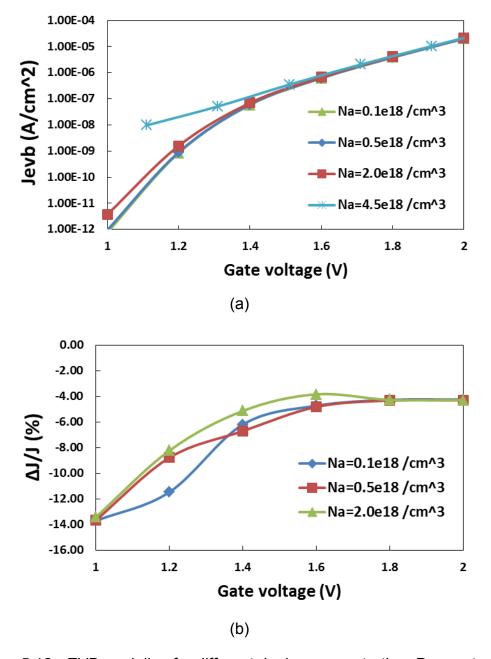

| Figure 5.12 | EVB modeling for different doping concentration. Parameters        |

|             | are the same as MOS tunneling current strain sensor in DC          |

|             | measurement. (a). Current density vs. gate voltage for EVB;        |

|             | (b). Sensitivity vs. gate current for EVB90                        |

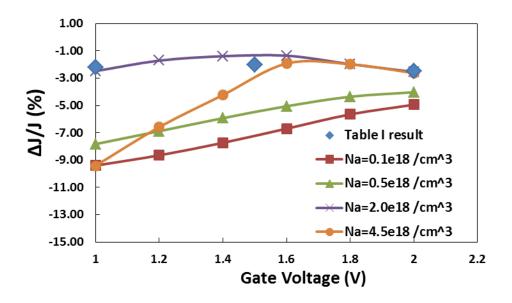

| Figure 5.13 | Total sensitivity vs. gate voltage at different doping                               |

|-------------|--------------------------------------------------------------------------------------|

|             | concentration. Parameters are the same as MOS tunneling                              |

|             | current strain sensor in DC measurement91                                            |

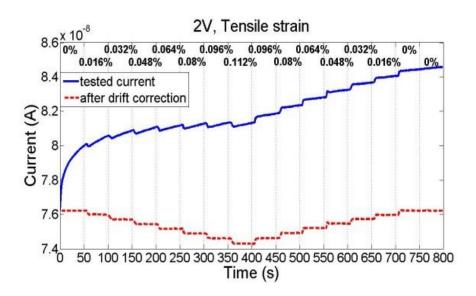

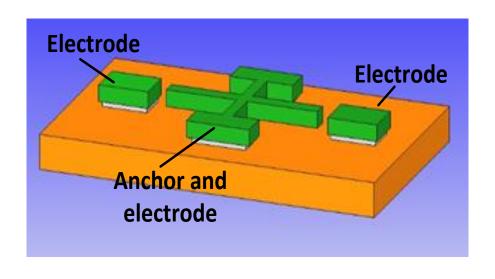

| Figure 6.1  | (a) 3D structure of a bulk acoustic RF resonator; (b) a                              |

|             | schematic showing working principle of longitudinal mode                             |

|             | beam resonator [10]98                                                                |

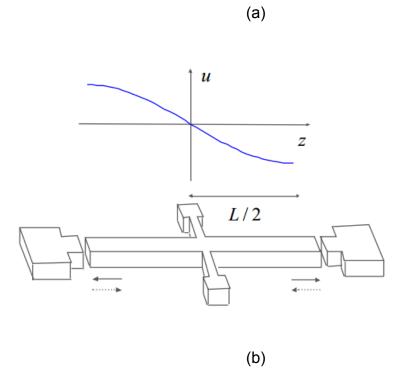

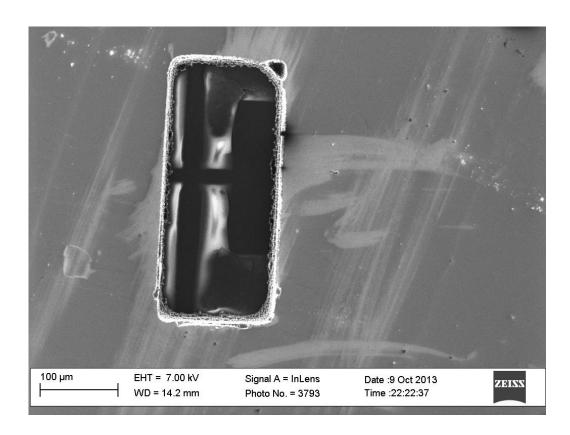

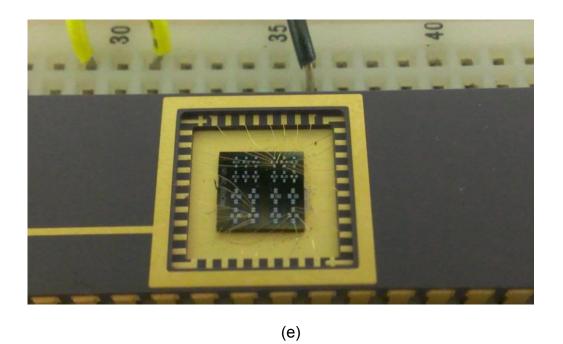

| Figure 6.2  | SEM picture and microscope picture of fabricated devices. (a)                        |

|             | SEM pictures for top layer before etching sacrificial layer of                       |

|             | SOI wafer. (b) Optical microscope picture for the final device                       |

|             | which is misaligned and not fully released. (c) SEM picture of                       |

|             | substrate layer for the final device which is misaligned. (d)                        |

|             | Optical microscope picture of the final device which is                              |

|             | misaligned but full released. (e) Packaged devices for testing.                      |

|             | 103                                                                                  |

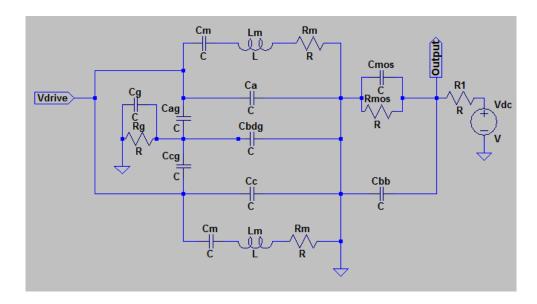

| Figure 6.3  | Equivalent circuit for MOS tunneling current sensing method.                         |

|             | 106                                                                                  |

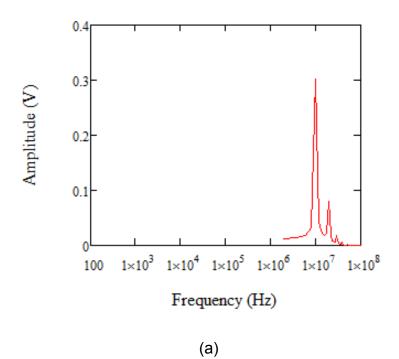

| Figure 6.4  | The output spectrum when $R \approx R1$ . (a) $\alpha \gg 1$ . (b) $\alpha \ll 1108$ |

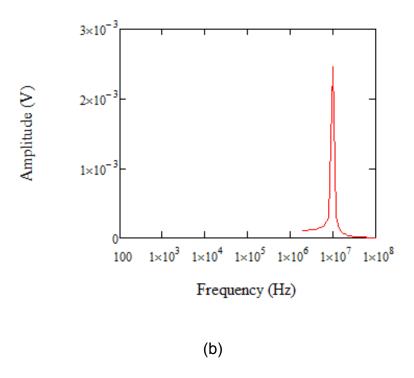

| Figure 6.5  | Schematic for measurement set up. (a) Capacitive sensing                             |

|             | method measurement set up. (b) MOS tunneling current                                 |

|             | sensing method measurement set up. (c) Picture of the                                |

|             | measurement set up                                                                   |

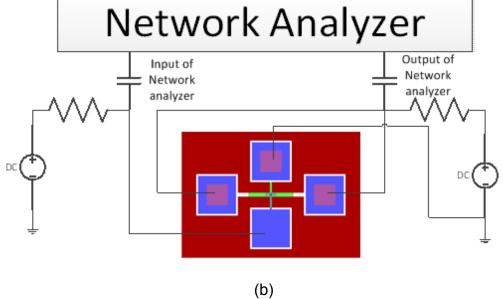

| Figure 6.6  | COMSOL modeling. The top bulk is contact which is 340 $\mu m$                        |

|             | (x) *340 $\mu$ m (y) *100 $\mu$ m (z). The bottom bulk is Silicon which              |

|             | is 6mm (x)* 6mm (y)* 400µm (z). The voltage is 1 V 114                               |

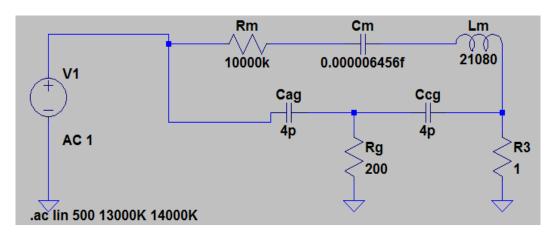

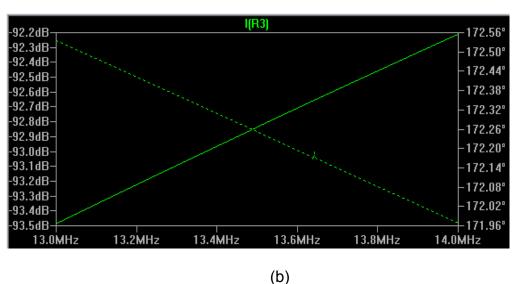

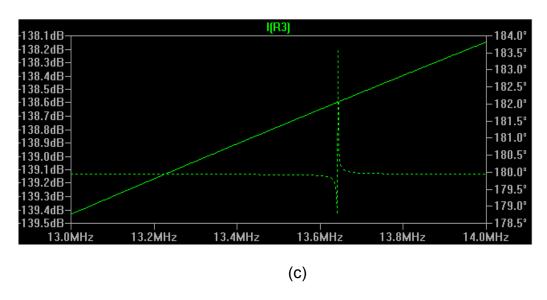

| Figure 6.7 | Spice modeling of substrate contact influence on capacitive   |

|------------|---------------------------------------------------------------|

|            | sensing method. (a) Equivalent circuit for capacitive sensing |

|            | method. R3 is the output. (b) Simulation result with $Rg =$   |

|            | 200 Ω. (c) Simulation result with $Rg = 1$ Ω                  |

| Figure 7.1 | Setup for sensitivity study at different stresses             |

| Figure 7.2 | Table of commercial and state-of-the-art R&D uncooled         |

|            | infrared bolometers121                                        |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

Since the research about the piezoresistance of silicon was published by Smith from Bell Telephones Laboratories in 1954, people have been studying the possibility of making micro sensors which have a superior performance to macro sensors at power consumption, reliability and size [1, 2]. According to different applications, microelectromechanical systems (MEMS) sensors can be cataloged into pressure sensors, accelerometers, gyroscopes, flow sensors, etc. Among these MEMS sensors, pressure sensors and accelerometers have a leading position in the markets [3]. The MEMS sensors can also be grouped to piezoresistive sensors, piezoelectric sensors, capacitivive sensors, etc. Piezoresistive sensors are among the earliest sensors, which are now being replaced by capacitive sensors.

Although MEMS pressure sensors and accelerometers have been widely researched and commercialized for decades, the recent increased demand for low power sensors is motivating research on new techniques. Portable electronics and biosensors in vivo usually require low power sensor to conserve power. Piezoresistive and capacitive sensing technologies are the most common technologies, which have been widely used to measure strain, pressure and acceleration [2, 4]. They both typically consume power from µW

to mW [5].

As for the piezoresistive sensors, to achieve low power consumption, the doping concentration of the piezoresistor has to be decreased For example, to have a minimum detectable strain of 0.001%, the doping concentration should be at least  $10^{16}$  atoms/cm<sup>3</sup> [6], and this doping concentration gives a resistivity of 1 ohm-cm. Information from [7] indicates that the MOS tunneling current through a 3.8 nm thick and 1 mm × 1 mm area  $SiO_2$  layer is around 1 nA at 1 V, which results in a resistivity of  $10^{13}$  ohm-cm. It is obvious a good alternative for low power sensing compared with piezoresistive technology [7]. Besides the power consumption, another disadvantage of piezoresistive technology is that it is not easy to control the doping profile of the piezoresistive layer especially for a very thin layer [1]. The  $SiO_2$  layer of the MOS tunneling sensor can be grown to less than 1 nm.

Capacitive sensors are the most common MEMS sensors now. They provide excellent low noise performance, high sensitivity, small temperature dependency and low power consumption. However parasitic capacitance of bond pads and small signal hinder the miniaturization of the capacitive sensors. Interface circuit is usually much more complex than piezoresistive sensors. The response is nonlinear, and both electrical and physical shielding is necessary [8, 9].

Besides adopting tunneling current through a MOS capacitor, tunneling sensors also employ tunneling current through an air gap between a tip and a plate which also have the merit of low power consumption. Pressure or acceleration induces displacement between the tip and the plate, which is read by the voltage or current changing [10-12]. The fabrication process of

this type of sensors is very complex. Like capacitive sensors, the response is also nonlinear. The interface circuit is very complex, which requires closed-loop control to maintain the gap distance. The reliability is also impacted due to deterioration of the tip.

The MOS tunneling sensors measure the current change induced by strain in silicon. The tunneling current is determined by the tunneling barrier between the silicon band edges and the gate dielectric band edges, as well as the effective mass. When a uniaxial strain is induced, the silicon band edges will be shift and split, which will change the tunneling barrier. As a result, the tunneling current changes with the strain. Detailed theory about the MOS tunneling sensors will be elaborated in the theory chapters.

Table 1 summarizes the advantages and the disadvantages of different MEMS sensors. The advantages are that the MOS tunneling current strain sensors are easy to fabricate and they are Complementary metal—oxide—semiconductor (CMOS) process compatible. However, the MOS tunneling current strain sensors are very sensitive to temperature like the piezoresistive sensors. Another disadvantage is that electrostatic discharge (ESD) protection is necessary, since the MOS tunneling current strain sensor is mainly a MOS capacitor.

Table 2 compares the gauge factor, the response linearity and the power consumption of different MEMS sensors. We can see that the gauge factor of MOS tunneling current strain sensor is in the same range of piezoresistive sensors, while its power consumption is much smaller. Here gauge factor is defined as  $GF = \frac{\Delta R/R}{\varepsilon} = \frac{\Delta I/I}{\varepsilon} = \frac{\Delta C/C}{\varepsilon}$ .

Table 1

Summaries of advantages and disadvantages for different sensing methods

|                      | Advantages                                                                                                                                     | Disadvantages                                                                                                                                 |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Piezoresistive       | Simple interface circuit                                                                                                                       | <ul> <li>Large temperature dependency</li> <li>Difficult to control Doping profile in the nm range</li> <li>High power consumption</li> </ul> |  |

| Capacitive           | <ul> <li>Excellent noise performance</li> <li>High sensitivity</li> <li>Small temperature dependency</li> <li>Low power consumption</li> </ul> | <ul> <li>Large area</li> <li>Complex circuit</li> <li>Need electrical and physical shield</li> <li>Non-linear</li> </ul>                      |  |

| Air gap<br>Tunneling | <ul><li>High sensitivity</li><li>Small temperature dependency</li></ul>                                                                        | <ul><li>Complex interface circuit</li><li>Tip deterioration</li><li>Non-linear</li></ul>                                                      |  |

| MOS tunneling        | <ul><li>Low power consumption</li><li>Easy to miniaturize</li></ul>                                                                            | <ul><li>Temperature dependent</li><li>Need ESD protection</li></ul>                                                                           |  |

Table 2

Summaries of gauge factor, linearity and power consumption for different sensing methods

| Principle             | Gauge      | Linearity | Power       |

|-----------------------|------------|-----------|-------------|

|                       | Factor     |           | consumption |

| Piezoresistive        | 100 [9]    | Linear    | 10 ~ 1000   |

|                       |            |           | uW [13, 14] |

| Capacitive            | 249 [15]   | Nonlinear | ~100 uW     |

|                       |            |           | [16]        |

| MOS Tunneling current | 35 [7, 17] | Linear    | 1~100 nW    |

| _                     |            |           | [7]         |

## 1.2 Relevance of the research

This dissertation demonstrates the first use of tunneling current sensing for a sensor that is based on the effects of strain in the semiconductor substrate. Prior efforts to create tunneling current sensors all utilize the tunneling current through a gap between two materials, and thus inherently measure the gap between the electrodes. In this dissertation, it is fundamentally the strain in the semiconductor, and not the gap, that is measured.

Along with metal-oxide-semiconductor field-effect transistor (MOSFET) scaling, gate oxide is scaled down and MOS tunneling current or gate leakage current arises [18-20]. Since then, a lot of research on this MOS tunneling current has been done in both experimental and theoretical way [21-26]. Most of this research is focused on the performance of new high-k dielectric materials by studying their MOS tunneling current. Strained MOSFET can improve carries' mobility, which has been studied extensively. In the same time, MOS tunneling current in strained MOSFET is also studied by several groups [27-30]. However in this research, MOS tunneling current is treated as an unpleasant phenomenon, and very few study are done to use this MOS tunneling current. For example, MOS tunneling current can be a very competitive alternative for low power strain sensors because of its high resistivity.

In the dissertation, it is the first time that a strain sensor based on MOS tunneling current is made and characterized. Parameters like noise, drift and sensitivity of MOS tunneling current strain sensor are characterized. It is found that noise is very small when MOS devices are in the inversion region.

We perform both DC measurement and AC measurement for the characterization. We find that an AC method using lock-in amplifier is more efficient to reduce noise than normal DC method.

To study sensitivity, a computationally efficient model for MOS tunneling current is built. Other groups only study ECB tunneling current for MOS in inversion region, which is enough for current density study. It is found that both the ECB and the EVB tunneling current must be considered when calculating the sensitivity for high doping concentrations and high voltages. The model fits our experiment very well.

A RF resonator based on MOS tunneling current strain sensor is also made. The first try was not successful. However, some tips to improve the design for future research are learned from this first try.

## 1.3 Outline of Dissertation

The research goals of this project are to characterize the properties of MOS tunneling sensors, solve problems hindering the performance of the MOS tunneling sensors and make a resonator based on the MOS tunneling current strain sensor as an application.

Chapter 2 introduces research history of tunneling current as well as theories of MOS tunneling current. Different types of MOS tunneling current are discussed, like Fowler-Nordheim tunneling, direct tunneling and trapassist-tunneling. In this chapter, an approximation method to calculate tunneling probability, the WKB method, is elaborated, as well as other basic formulas for MOS tunneling current. This WKB method will be used in the modeling for direct tunneling in Chapter 5.

Chapter 3 discusses strain effect on Silicon and MOS tunneling

current. First, the silicon band structure is briefly introduced. Then, the basic theory of strain tensor and stress tensor are introduced. In the end, strain effect on silicon band structure is discussed.

Chapter 4 characterizes the MOS tunneling current strain sensors experimentally using DC and AC method. The demonstration device is a cantilever beam. The MOS tunneling current strain sensor is fabricated near the fix end of the cantilever beam. Strain is induced by bending the free end. In the DC experiment, a semiconductor parameter analyzer is used to apply DC voltage and measure the DC current. During the AC experiment, a lock-in amplifier is used to isolate the MOS tunneling current. The reason of using AC method is to reduce noise in a faster way, which is very important especially when band width is considered for a sensor. From the experiments, it is found that the noise of NMOS tunneling current strain sensor in inversion region is much less than others.

Chapter 5 discusses modeling for NMOS tunneling current strain sensor in inversion region, which MOS tunneling current comprises two parts. One is the ECB tunneling current, in which electrons tunnel from conduction band. Another one is the EVB tunneling current, in which electrons tunnels from valence band. Sensitivity is extensively studied by modeling. In this chapter, it also shows that substrate doping concentration has a very large influence on MOS tunneling current.

Chapter 6 explores one application of MOS tunneling current strain sensor, which is a longitudinal bulk acoustic RF resonator. In this chapter, we design, simulate, fabricate and test a 13 MHz longitudinal bulk acoustic RF resonator. The difficulties of the fabrication are discussed in this chapter. The

resonator does not work. The reasons that may lead the resonator to fail are analyzed, and some modifications for future design are proposed.

In the end, Chapter 7 does a summary of this dissertation as well as a proposal of future research.

### CHAPTER 2

#### INTRODUCTION TO MOS TUNNELING CURRENT

## 2.1 History of quantum tunneling studying

This chapter gives a brief introduction of the history of quantum tunneling studying. Quantum tunneling is a phenomenon that a particle can penetrate a barrier which potential is higher than the particle's kinetic energy. Taking tunneling current as an example, the carrier (hole or electron) can surmount a potential barrier which is larger than its kinetic energy. This phenomenon is impossible in classic physics [18, 31].

After the discovery of natural alpha radioactivity in 1896, the law of exponential decay was established through the efforts of Elster, Rutherford, etc. [31, 32]. The theory of  $\alpha$ -radioactivity on the basis of quantum tunneling was proposed by Gamow in 1928. Classically, the particle confined to the nucleus lacks the energy to surmount the nucleus potential wall, but in quantum mechanics there is a probability at which a particle can tunnel out of the nucleus. Gamow solved a model potential for the nucleus by combining the attractive nuclear forces with the Coulomb repulsion and derived from a relationship between the half-life of the alpha-decay event process and the energy of the emission, the Geiger-Nuttall formula, which had been previously discovered empirically [32, 33]. At nearly the same time, the problem was also solved by Gurney and Condon qualitatively [32].

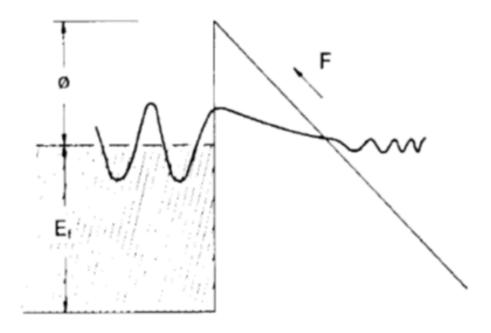

During the same period, tunneling was used to explain electron emission from cold metal by Fowler and Nordheim [34]. They proposed a one-dimensional model. Metal electrons are confined by a potential wall whose height is determined by the work function plus the Fermi energy, and the wall becomes triangle like and thinned with an applied high electric field. The electrons tunneling through the potential wall change with applied electric field. Along with this model, they came up with the famous Fowler-Nordheim equation [31],

$$J = AF^{2} \exp\left(-\frac{\sqrt{2m_{eff}}}{\hbar} \frac{4}{3} \frac{(\Phi_{B})^{\frac{3}{2}}}{qF}\right)$$

(2.1)

where  $\hbar$  is Planck's constant, q is electronic charge, F is electric field in the oxide,  $\Phi_B$  is barrier height, and  $m_{eff}$  is electron effective mass of the insulator.

Figure 2.1 FN tunneling (Figure is from [31]).

During the 1930s and 1940s, tunneling was proposed to explain the transportation of electrical contacts between two solids. In 1930, Frenkel [35]

proposed that the anomalous temperature independence of contact resistance between metals could be explained in terms of tunneling across a narrow vacuum separation. Holm and Meissner verified that by experiment. In 1932, Wilson [36], Frenkel and Joffe [37] and Nordheim [38] applied quantum mechanical tunneling to the interpretation of metal-semiconductor contacts (rectifiers), but it was late proved to be wrong about the direction of rectifying in reality.

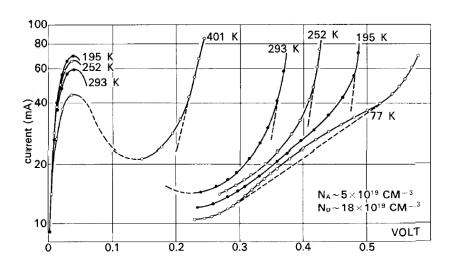

In 1950, with the development of diodes and transistors, the tunneling of electrons received new attention. In 1957 Esaki discovered the tunneling diode and this discovery proved the electron tunneling in solids conclusively [31]. The tunneling diode shows a negative resistive region as shown in Figure 2.2. This negative resistance can be interpreted by Figure 2.3. Both p and n type semiconductor are heavily doped to degeneration. When  $V_1$  is applied, electrons tunnel from n type conduction band to the p type valence band. When the voltage is increased to  $V_2$ , there is no energy level for electrons to tunnel, so the current decreases. As the voltage continuously increases, the tunnel diode works like a normal p-n diode.

Figure 2.2 Current-Voltage relation of a tunneling diode [31].

Figure 2.3 Band diagram of a tunneling diode at varies biases [31].

Tunneling was also researched in superconducting. In 1960, Giaever observed tunneling current between two conductors. At least one of the metals is a superconductor. This experiment enabled measurement of the energy gap in superconductors. This gap appears with Cooper pairs, and the gap plays an essential role in the BCS theory [39].

# 2.2 Different Types of Tunneling current in MOS capacitor

In the previous section, the history of research on quantum tunneling was reviewed briefly. This section will focus on MOS tunneling current. There are mainly three types of tunneling current in MOS capacitor, Fowler-Nordheim tunneling current, direct tunneling current and trap-assist-tunneling current.

As mentioned in the previous section, Fowler and Nordheim give a complete theory of Fowler-Norheim tunneling. However it is complicated. Lenzlinger and Snow simplify the equation by ignoring the effects of finite temperature and image-force barrier lowering [40]. The simplified equation is,

$$J = \frac{q^3 F^2}{16\pi^2 \hbar \Phi_B} \exp\left(-\frac{\sqrt{2m_{eff}}}{\hbar} \frac{4}{3} \frac{(\Phi_B)^{\frac{3}{2}}}{qF}\right)$$

(2.2)

where  $\hbar$  is Planck's constant, q is electronic charge, F is electric field in the oxide,  $\Phi_B$  is barrier height, and  $m_{eff}$  is electron effective mass of the insulator. Section 2.3 will derive this equation for Fowler-Norheim tunneling current. The reason that Equation 2.2 is derived is to get deep understanding of MOS tunneling current. In the same time, some concepts from Fowler-Norheim tunneling current are used to derive models for direct tunneling current, like WKB method.

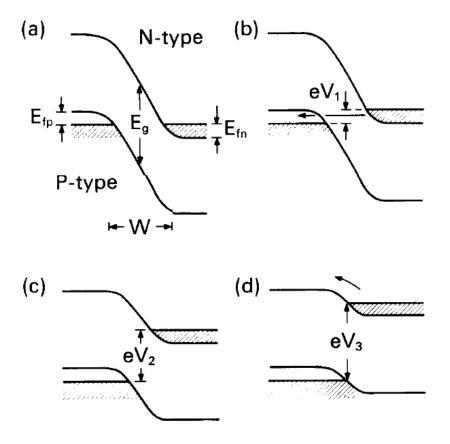

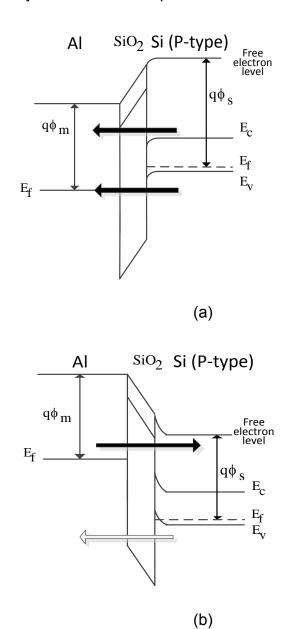

If the gate oxide is less than 4 nm, direct tunneling current will arise and become much larger than Fowler-Norheim tunneling current. As shown in the Figure 2.4 (a), when the gate voltage applied to the metal gate MOS devices is positive, there are two types of MOS tunneling current. One is ECB, where the electrons tunnel from the conduction band of silicon to aluminum; another one is EVB, where the electrons tunnel from the valence band of silicon to aluminum. When a negative gate voltage is applied to the gate as shown in Figure 2.4 (b), there are also two components of tunneling current. One is tunneling current from aluminum; another one is HVB, where the holes tunnel from the valence band of silicon to aluminum. The following chapters will focus on direct tunneling current, since the gate oxide of our MOS tunneling current strain sensor is less than 4 nm. Modeling of direct tunneling

current will be fully discussed in Chapter 5.

Figure 2.4 Illustration of direct tunneling in MOS structure. (a) positive bias; (b) negative bias.

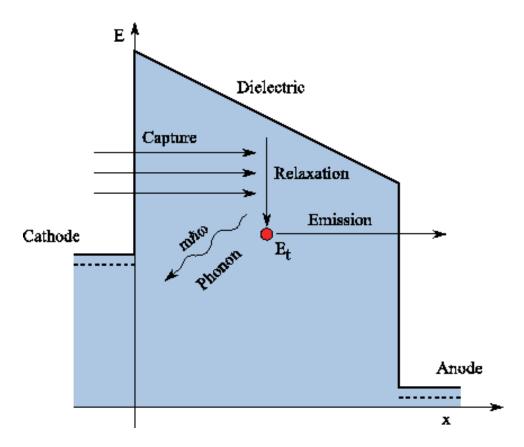

The last type of MOS tunneling current is the trap-assist-tunneling current, which is shown in Figure 2.5. Electrons from the cathode first tunnel into the traps in the insulator layer, and then tunnel into the anode from the traps in the insulator layer. Traps are usually defects in the insulator layer.

During the trapping procedure, electrons usually exchange energy with insulator lattice through phonons. Large tunneling current at large gate voltage usually will introduce defects in the insulator layer, which will eventually break the insulator layer. Trap-assist-tunneling current is commonly recognized as one of the sources of noise in MOS tunneling current.

Figure 2.5 Schematic illustrating the Trap-assist-Tunneling current. The figure is from [41].

# 2.3 Derivation of Fowler-Nordheim tunneling current equation in MOS structure

This section will derive Fowler-Nordheim tunneling Equation 2.2. The purpose of this derivation is to understand MOS tunneling current deeper. The derivation for Equation 2.2 will also be partly adopted in the derivation of

formula for direct tunneling current. The Tsu and Esaki model and the WKB method will be used to formulate a general equation for Fowler-Nordheim tunneling current. After the general equation is derived, by setting temperature to 0 K to remove temperature influence, Equation 2.2 can be derived.

# 2.3.1 Tsu and Esaki model for Fowler-Nordheim tunneling current equation

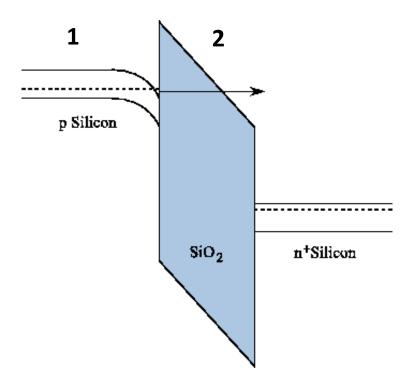

The formula for Fowler-Nordheim tunneling can be derived by the Tsu and Esaki model [42]. In the Tsu and Esaki model, as shown in Figure 2.6, it is assumed that the net tunneling current is determined by difference between the current flow from side 1 to side 2 ( $J_{1\rightarrow 2}$ ) and the current flow from side 2 to side 1 ( $J_{2\rightarrow 1}$ ).

Figure 2.6 Schematic illustrating Fowler-Nordheim Tunneling current. The figure is from [41].

$$dJ_{1\to 2} = qTC_1(k_x)v_xg_1(k_x)f_1(E)(1 - f_2(E))dk_x$$

$$dJ_{2\to 1} = qTC_2(k_x)v_xg_2(k_x)f_2(E)(1 - f_1(E))dk_x$$

(2.3)

The current density through the two interfaces depends on the perpendicular component of the wave vector  $k_x$ , the transmission coefficient TC, the perpendicular velocity  $v_x$ , the density of states  $g(k_x)$ , and the Fermi-Dirac distribution function f(E) at both sides of the barrier. For the Fowler-Nordheim tunneling, side 2 is the conduction band edge of  $SiO_2$ . Since  $SiO_2$  is an insulator,  $f_2(E)$  is almost 0 for energies above the conduction band edge of  $SiO_2$ . As a result,  $J_{2\rightarrow 1}$  is ignored and only  $J_{1\rightarrow 2}$  exists, which can be written as,

$$dJ = qTC(k_x)v_xg(k_x)f(E)dk_x$$

(2.4)

Here the density of states  $g(k_x)$  is

$$g(k_x) = \int_0^\infty \int_0^\infty g(k_x, k_y, k_z) dk_y dk_z$$

(2.5)

where  $g(k_x, k_y, k_z)$  denotes the three-dimensional density of states in the momentum space. Considering the quantized wave vector components within a cube of side length L,

$$\Delta k_x = \frac{2\pi}{L}, \ \Delta k_y = \frac{2\pi}{L}, \ \Delta k_z = \frac{2\pi}{L}$$

(2.6)

The density of states within the cube can be written as

$$g(k_x, k_y, k_z) = 2\frac{1}{\Delta k_x \Delta k_y \Delta k_z} \frac{1}{L^3} = \frac{1}{4\pi^3}$$

(2.7)

where the factor 2 comes from spin degeneracy. For the parabolic dispersion relation, the velocity and energy components in tunneling direction obey

$$v_{x} = \frac{1}{\hbar} \frac{\partial E}{\partial k_{x}} = \frac{\hbar k_{x}}{m_{eff}}, E_{x} = \frac{\hbar^{2} k_{x}^{2}}{2m_{eff}}, v_{x} dk_{x} = \frac{1}{\hbar} dE_{x}$$

(2.8)

Then Equation 2.4 can be rewritten as

$$dJ = \frac{q}{4\pi^3 \hbar} TC(E_x) dE_x \int_0^\infty \int_0^\infty f(E_x) dk_y dk_z$$

(2.9)

Next, let's transfer Equation 2.6 from Cartesian coordinate to Polar coordinate, which is

$$k_r = \sqrt{k_y^2 + k_z^2}, \theta = \arctan(\frac{k_z}{k_y})$$

$$k_y = k_r \cos(\theta), k_z = k_r \sin(\theta)$$

(2.10)

So the 3D dispersion equations can be rewritten as,

$$E_{r} = \frac{\hbar^{2}(k_{y}^{2} + k_{z}^{2})}{2m_{eff}} = \frac{\hbar^{2}k_{r}^{2}}{2m_{eff}}$$

$$E_{x} = \frac{\hbar^{2}k_{x}^{2}}{2m_{eff}}$$

(2.11)

As  $\int_0^\infty dk_y\,\int_0^\infty dk_z\,=\int_0^{2\pi}d\theta\int_0^\infty k_r\,dk_r$  , current density can be rewritten as

$$J = \frac{4\pi q m_{eff}}{h^3} \int_{E_{min}}^{E_{max}} TC(E_x) dE_x \int_0^\infty f(E) dE_r$$

$$= \frac{4\pi q m_{eff}}{h^3} \int_{E_{min}}^{E_{max}} TC(E_x) dE_x \int_{E_x}^\infty f(E) dE$$

(2.12)

Here  $E=E_r+E_x$ , so  $dE=dE_r$ . The lower limitation 0 of  $\int_0^\infty f(E)dE_r$  becomes  $E_x$  for  $\int_{E_x}^\infty f(E)dE$ . Putting the equation of Fermi-Dirac distribution  $f(E)=\frac{1}{e^{\frac{E-E_f}{(KT)}}+1}$  into Equation 2.12 results in

$$J = \frac{4\pi q m_{eff}}{h^{3}} \int_{E_{min}}^{E_{max}} TC(E_{x}) dE_{x} \int_{E_{x}}^{\infty} f(E) dE$$

$$= \frac{4\pi q m_{eff}}{h^{3}} \int_{E_{min}}^{E_{max}} TC(E_{x}) dE_{x} \int_{E_{x}}^{\infty} \frac{1}{e^{\frac{(E-E_{f})}{(k_{B}T)}} + 1} dE$$

$$= \frac{4\pi q m_{eff}}{h^{3}} \int_{E_{min}}^{E_{max}} TC(E_{x}) dE_{x} k_{B}T \left(-\ln\left(e^{\left(-\frac{E-E_{f})}{k_{B}T}\right)} + 1\right)\right|_{E_{x}}^{\infty}$$

$$= \frac{4\pi q m_{eff} k_{B}T}{h^{3}} \int_{E_{min}}^{E_{max}} TC(E_{x}) \ln\left(e^{\left(-\frac{E_{x}-E_{f}}{k_{B}T}\right)} + 1\right) dE_{x}$$

(2.13)

Now the general equation for Fowler-Nordheim tunneling current has been derived. In the next section, the formula for the tunneling probability  $TC(E_x)$  will be solved based on the WKB method.

#### 2.3.2 The WKB method

The WKB method is an approach to get an approximate solution for a linear partial differential equation with spatially varying coefficient. It is also known as the LG or Liouville–Green method [43]. In the tunneling cases, this spatially varying coefficient is the slowly varying potential in the gate oxide. In this section, general formula for the tunneling probability  $TC(E_x)$  will be deduced, which is then put into Equation 2.13 to get the final general Fowler-Nordheim tunneling current formula. The derivation can be found in any quantum mechanics book. It should be pointed out that WKB method is not only used for Fowler-Nordheim tunneling current equation, it is also used for direct tunneling current equation. This will be elaborated in the following sections.

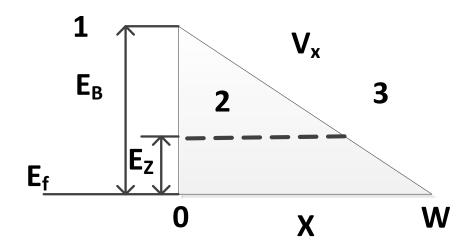

For simplicity, as shown in Figure 2.7, only formula in one dimension is considered, though the WKB method can be applied to 3D. Electrons move along x direction. Here electrons tunnel from left to right. There are three regions in this schematic. Region 1 is the incident region, region 2 is the

forbidden region and region 3 is the transmitted region. Here  $E_f$  is the Fermi level,  $E_B$  is the work function, W is the thickness of the gate oxide,  $V_x$  is the linear varying potential in the gate oxide.  $E_z$  is forbidden energy at the position of Z along x direction.

Figure 2.7 Schematic Illustrating for the WKB method.

Schrodinger equation can be solved under these boundary conditions.

The Schrodinger equation for an electron moving along x direction is

$$-\frac{\hbar^2}{2m}\frac{d^2\psi}{d^2x} + V(x)\psi(x) = E\psi(x)$$

(2.14)

Or

$$\frac{d^2\psi}{d^2x} + \frac{1}{\hbar^2}p^2(x)\psi(x) = 0$$

(2.15)

where p(x) is the classical momentum along x direction,  $p(x) = \sqrt{2m(E - V(x))}$ . m is the effective mass along the tunneling direction, which is x direction here. For the forbidden region which is the gate oxide, V(x) varies linearly. It is easy to obtain the wave functions for the incident region and transmitted region respectively,

$$\psi_1(x) = \psi_{incident}(x) + \psi_{reflected}(x) = Ae^{ip_0x/\hbar} + Be^{-ip_0x/\hbar}$$

(2.16)

$$\psi_3(x) = \psi_{transmitted}(x) = Te^{ip_0 x/\hbar}$$

(2.17)

where  $\psi_1(x)$  is the wave function in the incident region and  $\psi_3(x)$  is the wave function in the transmitted region. A, B and T are the amplitudes of the incident, reflected and transmitted waves respectively.  $p_0 = \sqrt{2mE}$  is the momentum. The solution of the WKB method for the forbidden region assumes a form like,

$$\psi(x) = A(x)e^{iS(x)/\hbar} \tag{2.18}$$

where A(x) is the amplitude and S(x) is the phase, and they both are real functions. Substituting (2.18) into (2.15), we get

$$A\left[\frac{\hbar^2}{A}\frac{d^2\psi}{d^2x} - (\frac{dS}{dx})^2 + p^2(x)\right] + i\hbar\left[2\frac{dA}{dx}\frac{dS}{dx} + A\frac{d^2S}{d^2x}\right] = 0$$

(2.19)

Only when both the real part and the imaginary part equal to 0, Equation 2.19 makes sense. Besides, since  $\hbar$  is a small number,  $\frac{\hbar^2}{A}\frac{d^2\psi}{d^2x}$  can be neglected. Thus,

$$\frac{dS}{dx} = \pm p(x) = \pm \sqrt{2m(E - V)} \tag{2.20}$$

$$2\frac{dA}{dx}\frac{dS}{dx} + A\frac{d^2S}{d^2x} = 0$$

(2.21)

Integrating Equation 2.20 gives

$$S(x) = \pm \int \sqrt{2m(E - V)} dx$$

(2.22)

Rewriting Equation 2.21 yields

$$2\left(\frac{d}{dx}\ln A\right)p(x) + \frac{d}{dx}p(x) = 0$$

$$\xrightarrow{\text{yields}} \frac{d}{dx}(2\ln A + \ln p) = 0$$

$$\xrightarrow{\text{yields}} A = \frac{C}{\sqrt{|p(x)|}}$$

(2.23)

where  $\mathcal{C}$  is a constant. Inserting Equation 2.22 and 2.23 into 2.18 indicates

$$\psi_{\pm}(x) = \frac{C_{\pm}}{\sqrt{|p(x)|}} \exp\left(\pm \frac{i}{\hbar} \int_{x_1}^x p(x') dx'\right)$$

(2.24)

Consider that E<V, which is known as the classically forbidden region, then (2.24) becomes,

$$\psi_{2}(x) = \frac{C}{\sqrt{|p(x)|}} \exp\left(-\frac{1}{\hbar} \int_{x_{1}}^{x} |p(x')| \, dx'\right) + \frac{D}{\sqrt{|p(x)|}} \exp\left(\frac{1}{\hbar} \int_{x_{1}}^{x} |p(x')| \, dx'\right)$$

(2.25)

Since  $\exp\left(\frac{i}{\hbar}\int_{x_1}^x |p(x')|dx'\right)$  increase exponentially with x, which is impossible in Physics, it is neglected for  $\psi_2(x)$ . Then,

$$\psi_2(x) = \frac{C}{\sqrt{|p(x)|}} exp\left(-\frac{1}{\hbar} \int_{x_1}^x |p(x')| \, dx'\right)$$

(2.26)

Now the wave functions for three regions (incident region, forbidden region and transmitted region) are derived. The probability of tunneling (TC) can be expressed as

$$TC = \frac{v_{trans}}{v_{inc}} \frac{|\psi_{trans}(x)|^2}{|\psi_{inc}(x)|^2} = \frac{|T|^2}{|A|^2}$$

(2.27)

where the speed of incident  $(v_{inc})$  and the speed of transmitted  $(v_{trans})$  particles are equal. To get TC,  $\psi_{inc}(x)$  and  $\psi_{trans}(x)$  must be solved. By using the continuity relations between incident region and forbidden region  $\psi_1(x_1)$  =

$\psi_2(x_1)$  and  ${\psi_1}'(x_1) = {\psi_2}'(x_1)$  indicates

$$Ae^{ip_0x_1/\hbar} + Be^{-ip_0x_1/\hbar} = \frac{C}{\sqrt{|p(x_1)|}}$$

(2.28)

$$\frac{i}{\hbar} (Ae^{ip_0x_1/\hbar} - Be^{-ip_0x_1/\hbar}) = -\frac{C|p(x_1)|}{\hbar\sqrt{|p(x_1)|}}$$

(2.29)

Adding Equation 2.28 and 2.29, it yields

$$C = 2A\sqrt{|p(x_1)|}/(1-\sqrt{|p(x_1)|}/ip_0)$$

(2.30)

Using the continuity relations between forbidden region and transmitted region  $\psi_2(x_2)=\psi_3(x_2)$  and  ${\psi_2}'(x_2)={\psi_3}'(x_2)$  can obtain,

$$\frac{C}{\sqrt{|p(x_2)|}} \exp\left(-\frac{1}{\hbar} \int_{x_1}^{x_2} |p(x')| \, dx'\right) = Te^{ip_0 x_2/\hbar}$$

(2.31)

$$-\frac{|p(x_2)|C}{\hbar\sqrt{|p(x_2)|}}\exp\left(-\frac{1}{\hbar}\int_{x_1}^{x_2}|p(x')|\,dx'\right) = \frac{ip_0}{\hbar}Te^{ip_0x_2/\hbar}$$

(2.32)

Inserting Equation 2.31 into 2.30 results in

$$\frac{T}{A} = \frac{2}{1 - \sqrt{|p(x_1)|}/ip_0} \sqrt{\frac{p(x_1)}{p(x_2)}} \exp(ip_0(x_1 - x_2)/\hbar) \exp\left(-\frac{1}{\hbar} \int_{x_1}^{x_2} |p(x')| dx'\right)$$

(2.33)

So the tunneling probability is

$$TC = \left| \frac{T}{A} \right|^{2}$$

$$= \frac{4}{\frac{|p(x_{2})|}{|p(x_{1})|} + \frac{|p(x_{1})||p(x_{2})|}{p_{0}^{2}}} \exp\left(-\frac{2}{\hbar} \int_{x_{1}}^{x_{2}} \sqrt{2m(V(x) - E)} \, dx\right)$$

$$\sim \exp\left(-\frac{2}{\hbar} \int_{x_{1}}^{x_{2}} \sqrt{2m(V(x) - E)} \, dx\right)$$

(2.34)

Now the general tunneling probability from WKB method is obtained,

which is Equation 2.34. Next TC for Fowler-Nordheim tunneling current will be derived. For Fowler-Nordheim tunneling current, the potential barrier is like a triangle, so the tunneling probability for the Fowler-Nordheim tunneling current can be calculated. As shown in Fig. 2.7, it is assumed that the thickness of the barrier is W, the barrier height is  $E_B$ , the tunneling length of an energy of  $E_Z$  (which is relative to  $E_f$ ) is Z. Thus,

$$V(x) = \left(1 - \frac{x}{W}\right)E_B + E_f \tag{2.35}$$

So TC can be derived as

$$TC(E_Z + E_f) = \exp\left(-\frac{\sqrt{8m}}{\hbar} \int_0^Z \sqrt{(1 - \frac{x}{W})E_B - E_Z} \, dx\right)$$

$$= \exp\left(-\frac{\sqrt{8m}}{\hbar} \left[-\frac{2W}{3E_B} \left((1 - \frac{x}{W})E_B - E_Z\right)^{3/2}\right]_0^Z\right]$$

$$= \exp\left(\frac{\sqrt{8m}}{\hbar} \frac{2W}{3E_B} \left[\left((1 - \frac{Z}{W})E_B - E_Z\right)^{\frac{3}{2}} - (E_B - E_Z)^{\frac{3}{2}}\right]\right)$$

$$= \exp\left(\frac{\sqrt{8m}}{\hbar} \frac{2W}{3E_B} \left[-(E_B - E_Z)^{\frac{3}{2}}\right]\right)$$

$$\cong \exp\left(-\frac{2\sqrt{8mE_B}W}{3\hbar} \left(1 - \frac{3E_Z}{2E_B}\right)\right)$$

$$= \exp\left(-\frac{2\sqrt{8mE_B}W}{3\hbar} \exp\left(\frac{\sqrt{8mE_B}WE_Z}{\hbar E_B}\right)\right)$$

$$= T_0 \exp\left(\frac{E_Z}{E_0}\right)$$

(2.36)

where

$$T_0 = \exp\left(-\frac{2\sqrt{8mE_B}W}{3\hbar}\right) \tag{2.37}$$

$$E_0 = \frac{\hbar E_B}{W\sqrt{8mE_B}}$$

Inserting Equation 2.36 into 2.13 gives

$$J = \frac{4\pi q m_{eff} k_B T}{h^3} T_0 \int_{E_{min}}^{E_{max}} exp(\frac{E_x - E_f}{E_0}) \ln\left(e^{\left(-\frac{E_x - E_f}{k_B T}\right)} + 1\right) dE_x$$

(2.38)

Here  $E_x-E_f=E_Z$ . We assume  $E_{min}=-\infty$  and  $E_{max}=+\infty$ . We can obtain

$$J = \frac{4\pi q m_{eff} k_B T}{h^3} T_0 \int_{-\infty}^{+\infty} \exp(\frac{E_x - E_f}{E_0}) \ln\left(e^{\left(-\frac{E_x - E_f}{k_B T}\right)} + 1\right) dE_x$$

(2.39)

Using the variable change  $u=e^{\left(-\frac{E_{x}-E_{f}}{k_{B}T}\right)}$  and  $du=\frac{-1}{k_{B}T}udE_{x}$  gives the current density,

$$J = \frac{4\pi q m_{eff} k_B T}{h^3} T_0(-k_B T) \int_{+\infty}^{0} u^{-\frac{k_B T}{E_0} - 1} \ln(u + 1) du$$

$$= \frac{4\pi q m_{eff} k_B T}{h^3} T_0(k_B T) \int_{0}^{+\infty} u^{-\frac{k_B T}{E_0} - 1} \ln(u + 1) du$$

$$= \frac{4\pi q m_{eff} k_B T}{h^3} T_0(k_B T) \frac{\pi}{\left(\frac{k_B T}{E_0}\right) \sin(\frac{k_B T}{E_0} \pi)}$$

$$= \frac{4\pi q m_{eff} (k_B T)^2}{h^3 \left(\frac{k_B T}{E_0}\right)^2} T_0 \frac{\left(\frac{k_B T}{E_0}\right) \pi}{\sin(\frac{k_B T}{E_0} \pi)}$$

(2.40)

Since

$$T_{0} = \exp\left(-\frac{2\sqrt{8mE_{B}}W}{3\hbar}\right)$$

$$= \exp\left(\frac{\sqrt{8m}}{\hbar} \frac{2W}{3E_{B}} \left[-(E_{B})^{\frac{3}{2}}\right]\right)$$

(2.41)

and

$$E_R = qFW (2.42)$$

where F is the electrical field in the insulator, Equation 2.40 can be written as

$$J = \frac{4\pi q m_{eff} \left(\frac{\hbar E_B}{W\sqrt{8m_{eff}E_B}}\right)^2}{\hbar^3 8\pi^3} \exp\left(-\frac{\sqrt{2m_{eff}}}{\hbar} \frac{4}{3} \frac{(E_B)^{\frac{3}{2}}}{qF}\right) \frac{\left(\frac{k_B T}{E_0}\right) \pi}{\sin(\frac{k_B T}{E_0}\pi)}$$

$$= \frac{q^3 F^2}{16\pi^2 \hbar E_B} \exp\left(-\frac{\sqrt{2m_{eff}}}{\hbar} \frac{4}{3} \frac{(E_B)^{\frac{3}{2}}}{qF}\right) \frac{\left(\frac{k_B T}{E_0}\right) \pi}{\sin(\frac{k_B T}{E_0}\pi)}$$

(2.43)

For the special case of T=0 K, the classic Fowler-Nordheim tunneling current formula without temperature influence can be obtained

$$J = \frac{q^3 F^2}{16\pi^2 \hbar E_B} \exp\left(-\frac{\sqrt{2m_{eff}}}{\hbar} \frac{4}{3} \frac{(E_B)^{\frac{3}{2}}}{qF}\right)$$

(2.44)

Now the derivation for the Fowler-Nordheim tunneling current is completed, but several things should be paid attention to,

- The electrons in the emitted electrode are assumed to be free Fermi gas.

- 2) The barrier lowering due to the image force is neglected.

- 3) The effective mass in the formula is the effective mass in the forbidden region. Since the effective mass is related to energy which varies in the forbidden region slowly, it is usually averaged through the whole region.

# 2.4 Direct tunneling in MOS structure

Direct tunneling is a mechanism that the electrons tunnel directly into the other electrode instead of the conduction band of the insulator. Taking MOS structure as an example, when the thickness of insulator (SiO<sub>2</sub>) is less than 4 nm, direct tunneling dominates. However when the thickness of insulator is more than 4 nm, Fowler-Nordheim tunneling current dominates. There are several different components of a direct tunneling current, depending on the gate voltage polarization and amplitude of voltages and the material of the conductors.

# 2.4.1 Derivation of the direct tunneling formula

During the derivation of Fowler-Nordheim tunneling current formula, we use WKB method to calculate the tunneling probability which is only valid when the oxide layer is thicker than 4 nm. When the thickness of the oxide layer is less than 1 nm, the assumption that the barrier changes slowly, which is the fundamental assumption of the WKB method, may not be very accurate. For gate oxide thickness larger than 1 nm, we still can use WKB method for *TC*. There are also several alternative methods to derive the direct tunneling formula. The results from these methods are close and fit to the measurement well [44]. Here we only briefly introduce the transfer matrix method to calculate the tunneling probability.

The general direct tunneling current formula can also be derived by the Tsu and Esaki model. When deriving the FN tunneling formula, it is assumed that  $J_{2\rightarrow1}$  (the current from the conduction band of SiO<sub>2</sub>) can be ignored and obtain Equation 2.13. However for the direct tunneling,  $J_{2\rightarrow1}$  (the current from the conduction band of substrate) is kept, so the total net tunneling current is,

$$J = J_{2\to 1} - J_{1\to 2} = \frac{4\pi q m_{eff} k_B T}{h^3} \int_{E_{min}}^{E_{max}} TC(E_x) \ln \left( \frac{e^{\left(-\frac{E_x - E_{f2}}{k_B T}\right)} + 1}{e^{\left(-\frac{E_x - E_{f1}}{k_B T}\right)} + 1} \right) dE_x \quad (2.45)$$

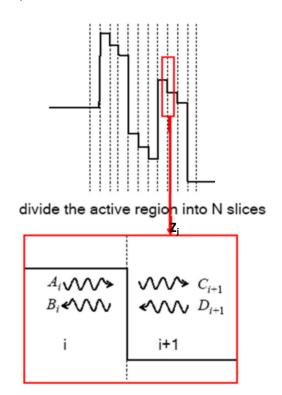

where  $E_{f1}$  or  $E_{f2}$  is the Fermi level in the side 1 or 2. The next step is to find  $TC(E_x)$  using transfer matrix method. To apply transfer matrix method, the whole scattering barrier is partitioned in to many small slab regions, and in every slab region the barrier is assumed constant so that the Schrodinger equation can be solved analytically. The transfer matrix between two neighboring slabs is obtained by applying the continuity of the wave functions and their derivatives at the boundaries, and the overall transfer matrix is obtained by multiplying all these transfer matrices. For example, a barrier shown in Figure 2.8 can be divided into small slabs. The wave functions of slab j and slab j+1 are,

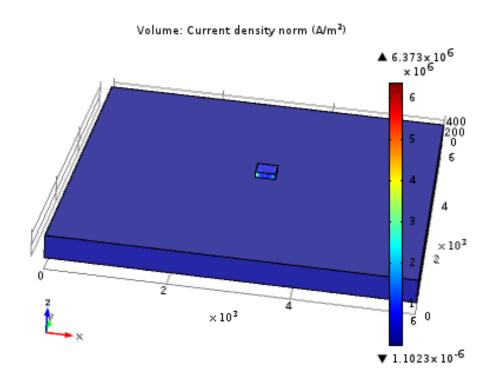

Figure 2.8 Transfer matrix method [45].

$$\psi_{j}(x) = A_{j}e^{ik_{j}x} + B_{j}e^{-ik_{j}x}$$

(2.46)

$$\psi_{j+1}(x) = C_{j+1}e^{ik_{j+1}x} + D_{j+1}e^{-ik_{j+1}x}$$

(2.47)

Using the continuity conditions,

$$\psi_{j}(Z_{j}) = \psi_{j+1}(Z_{j})$$

$$\frac{\partial \psi_{j}(Z_{j})}{\partial Z} = \frac{\partial \psi_{j+1}(Z_{j})}{\partial Z}$$

(2.48)

The transfer matrix  $T_i$  is

$$\begin{bmatrix} C_{j+1} \\ D_{j+1} \end{bmatrix} = T_j \begin{bmatrix} A_j \\ B_j \end{bmatrix}$$

(2.49)

Therefore, the overall transfer matrix TC is

$$TC = T_1 T_2 T_3 \cdots T_j \cdots T_{max} \tag{2.50}$$

It is obvious that we cannot get an analytic solution from transfer matrix method.

# 2.5 Summary

This chapter reviews the history of tunneling from the early 20 centuries' research on alpha radioactivity to recently extensive research on superconducting. Then MOS tunneling current is elaborated. First, three types of MOS tunneling current, Fowler-Nordheim tunneling current, direct tunneling current and trap-assist-tunneling current are introduced. Since the Fowler-Nordheim tunneling current and direct tunneling current are the main tunneling current in MOS capacitor, to deep understand these two types of tunneling current, the general tunneling current formula for these two types of tunneling current are derived. Two approaches to solve tunneling probability are discussed, which are WKB method and transfer matrix method. WKB method can be used in both Fowler-Nordheim tunneling current and direct tunneling current (which gate oxide thickness is larger than 1 nm and less than 4 nm), while transfer matrix method is mainly used in direct tunneling

current. The advantage of the WKB method is its simplicity and it is analytically expressed.

As shown in Chapter 4, the proposed experimental device's gate oxide is less than 4 nm, so direct tunneling current dominates. Therefore in Chapter 5, how to solve direct tunneling current based on this chapter as well as other factors like inversion layer energy quantization will be elaborated in detail.

#### **CHAPTER 3**

#### STRAIN EFFECTS IN SILICON

Chapter 2 discusses MOS tunneling current, especially the Fowler-Nordheim tunneling current and direct tunneling current. In this chapter, strain effects in silicon will be introduced. First, silicon band structure will be discussed, and then some concepts about stress and strain will be investigated. In the end, how strain affects band structure and eventually MOS tunneling current will be explored.

#### 3.1 Silicon band structure

To calculate the band structure of a crystal like Silicon, the single electron Schrodinger equation must be solved [46],

$$H\psi(\mathbf{r}) = \left(\frac{p^2}{2m} + V(\mathbf{r})\right)\psi(\mathbf{r}) = E\psi(\mathbf{r})$$

(3.1)

where  $V(\mathbf{r})$  is the effective crystal potential, m is the effective mass.  $\mathbf{r}$  is the movement direction of electrons. The difference among different materials is  $V(\mathbf{r})$  and m. It is the single crystal silicon that is studied here. A crystal is constructed of replicas of lattice, which is an array of atoms or molecules repeating periodically in three dimensions. The lattice of silicon is face centered cubic (FCC) as shown in Figure 3.1. The FCC lattice is point symmetry, and there are a total of 48 symmetry operations. Since the arrangement of atoms influence effective crystal potential, the effective crystal

potential is also periodic and symmetric. Here we define lattice constant is a.

Figure 3.1 FCC lattice [47].

The band structure of Silicon solved by the Schrodinger equation is shown in Figure 3.2, which is constructed in the reciprocal space (k space) of the real lattice space. The reciprocal lattice for an FCC lattice is a body centered cubic (BCC) lattice. Due to the translation of the reciprocal lattice, it is conventionally only plotting the energy levels in the first Brillouin zone, which is defined as the space enclosed by the planes perpendicular to and bisecting the lines connecting a reciprocal lattice point and its neighbors. The first Brillouin zone of Silicon is shown in Figure 3.3. In the figure,  $\Gamma$  point is the center point of the first Brillouin zone. X point is located at  $2\pi/a(0, 1, 0)$

labeling the center of the square surfaces, and the direction from  $\Gamma$  to X is named as  $\Delta$ . L point is located at  $2\pi/a(0.5, 0.5, 0.5)$  labeling the center of the hexagonal surfaces, and the direction from  $\Gamma$  to L is labeled as  $\Lambda$ . Thus, the valley of valence band of Silicon is at the point of  $\Gamma$ , and its valley of conduction band is located between  $\Gamma$  and X along the direction of  $\Delta$ . Since there are six equivalent directions of  $\Delta$ , the valley of conduction band is six folded degenerated. The band gap is 1.12 ev for silicon [46, 48].

Figure 3.2 Band structure of Silicon [49].

Figure 3.3 The first Brillouin zone of Silicon [50].

The band structure and the first Brillouin zone are based on the crystal lattice free of stress. The following sections will show how the stresses change the band structure of silicon.

## 3.2 Stress tensor

Tensors describe linear relations between two physical quantities. It can be a scalar, a vector or a matrix, depending on the order (rank) of the tensor. Stress is a force upon a unit area. The stress on an infinitesimal volume cube is shown in Figure 3.4.  $\sigma_{xx}$ ,  $\sigma_{yy}$  and  $\sigma_{zz}$  are normal stresses, which are along the direction of surface.  $\sigma_{xy}$  is defined as the shear stress along x direction at the surface which out-of-plane direction is along y direction. According to the force equilibrium principal,  $\sigma_{xy} = \sigma_{yx}$  and  $\sigma_{zy} = \sigma_{yz}$ .

Figure 3.4 Stress components on the surfaces of an infinitesimal cube [51].

The Stress tensor is a second rank tensor of nine elements, including all of the normal stress and shear stress, which equals to,

$$\sigma = \begin{bmatrix} \sigma_{xx} & \sigma_{xy} & \sigma_{xz} \\ \sigma_{yx} & \sigma_{yy} & \sigma_{yz} \\ \sigma_{zx} & \sigma_{zy} & \sigma_{zz} \end{bmatrix}$$

(3.2)

## 3.3 Strain tensor

Strain is caused by deformation and representing the relative displacement between lattice point. The strain tensor is defined as following,

$$\varepsilon = \begin{bmatrix} \varepsilon_{xx} & \varepsilon_{xy} & \varepsilon_{xz} \\ \varepsilon_{yx} & \varepsilon_{yy} & \varepsilon_{yz} \\ \varepsilon_{zx} & \varepsilon_{zy} & \varepsilon_{zz} \end{bmatrix}$$

(3.3)

where  $\varepsilon_{xx}$ ,  $\varepsilon_{yy}$  and  $\varepsilon_{zz}$  represent the distortion of along the length, the other parts represent the distortion created by rotation. Like stress tensor, according to equilibrium principal,  $\varepsilon_{xy}=\varepsilon_{yx}$ ,  $\varepsilon_{xz}=\varepsilon_{zx}$  and  $\varepsilon_{yz}=\varepsilon_{zy}$ . Therefore, six elements should be enough to express stress tensor and strain tensor. We can rewrite the stress and strain tensors to,

$$\varepsilon = \begin{bmatrix} \varepsilon_{xx} & \varepsilon_{yy} & \varepsilon_{zz} & \varepsilon_{yz} & \varepsilon_{zx} & \varepsilon_{xy} \end{bmatrix}$$

(3.4)

$$\sigma = \begin{bmatrix} \sigma_{xx} & \sigma_{yy} & \sigma_{zz} & \sigma_{yz} & \sigma_{zx} & \sigma_{xy} \end{bmatrix}$$

(3.5)

In the linear elastic body, Hooke's law introduces a linear relation between stress and strain, so we can get a matrix expression for the relation between stress and strain, which is shown below,

$$\begin{bmatrix}

\sigma_{xx} \\

\sigma_{yy} \\

\sigma_{zz} \\

\sigma_{yz} \\

\sigma_{zx} \\

\sigma_{xy}

\end{bmatrix} =

\begin{bmatrix}

C_{11} & C_{12} & C_{12} & 0 & 0 & 0 \\

C_{12} & C_{11} & C_{12} & 0 & 0 & 0 \\

C_{12} & C_{12} & C_{11} & 0 & 0 & 0 \\

0 & 0 & 0 & C_{44} & 0 & 0 \\

0 & 0 & 0 & 0 & C_{44} & 0 \\

0 & 0 & 0 & 0 & 0 & C_{44}

\end{bmatrix}

\begin{bmatrix}

\varepsilon_{xx} \\

\varepsilon_{yy} \\

\varepsilon_{zz} \\

\varepsilon_{yz} \\

\varepsilon_{zx} \\

\varepsilon_{xy}

\end{bmatrix}$$

(3.6)

where the coefficients  $C_{ij}$  are called elastic stiffness constants. The elastic stiffness constants are determined by materials. It has to be pointed out that there are only three independent components for the cubic crystal for its high symmetry. In most cases, it is more common to use the inverse of the elastic stiff tensor, the compliance tensor which is defined as,

$$S = \begin{bmatrix} S_{11} & S_{12} & S_{12} & 0 & 0 & 0 \\ S_{12} & S_{11} & S_{12} & 0 & 0 & 0 \\ S_{12} & S_{12} & S_{11} & 0 & 0 & 0 \\ 0 & 0 & 0 & S_{44} & 0 & 0 \\ 0 & 0 & 0 & 0 & S_{44} & 0 \\ 0 & 0 & 0 & 0 & 0 & S_{44} \end{bmatrix}$$

$$(3.7)$$

where  $S_{ij}$  is called the compliance. Therefore, the new relation between strain and stress is

$$\varepsilon = S\sigma \tag{3.8}$$

From this relation listed above, strain (or stress) can be caculated, if the stress (or strain) of a material is known.

A strain tensor can be decomposed into three separate tensors,

$$\begin{bmatrix} \varepsilon_{xx} & \varepsilon_{xy} & \varepsilon_{xz} \\ \varepsilon_{yx} & \varepsilon_{yy} & \varepsilon_{yz} \\ \varepsilon_{zx} & \varepsilon_{zy} & \varepsilon_{zz} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} \varepsilon_{xx} + \varepsilon_{yy} + \varepsilon_{zz} & 0 & 0 \\ 0 & \varepsilon_{xx} + \varepsilon_{yy} + \varepsilon_{zz} & 0 \\ 0 & 0 & \varepsilon_{xx} + \varepsilon_{yy} + \varepsilon_{zz} \end{bmatrix}$$

$$+ \frac{1}{3} \begin{bmatrix} 2\varepsilon_{xx} - (\varepsilon_{yy} + \varepsilon_{zz}) & 0 & 0 \\ 0 & 2\varepsilon_{yy} - (\varepsilon_{zz} + \varepsilon_{xx}) & 0 \\ 0 & 0 & 2\varepsilon_{zz} - (\varepsilon_{xx} + \varepsilon_{yy}) \end{bmatrix}$$

$$+ \begin{bmatrix} 0 & \varepsilon_{xy} & \varepsilon_{xz} \\ \varepsilon_{yx} & 0 & \varepsilon_{yz} \\ \varepsilon_{zx} & \varepsilon_{zy} & 0 \end{bmatrix}$$

$$(3.9)$$

where the first one describes the effect of a hydrostatic strain, and the last two tensors represent the shear strain. For a cubic crystal, when a uniaxial stress is applied along <100> axes, only the first type of shear strain is introduced. When there are stresses along <110> or <111>, the second type of shear strain exists plus first type of shear strain.

The hydrostatic strain only changes the volume of the cubic, the first shear strain changes the length of cubic along x, y and z, and the second shear strain rotates the axes. When only the first type shear strain is non-zero and  $\varepsilon_{xx} \neq \varepsilon_{yy} \neq \varepsilon_{zz}$ , the cubic deforms to an orthorhombic. If two of them equal, the orthorhombic degenerates to a tetragonal. When the second type shear strain exists and  $\varepsilon_{xy} \neq \varepsilon_{yz} \neq \varepsilon_{xz}$  the cubic becomes triclinic. However, if two of the shear strain are zero, the triclinic degenerates to an orthorhombic. For example, when a biaxial stress is applied, after decomposing the strain tensor, only the hydrostatic and the first type shear strain is not zero, plus  $\varepsilon_{xx} = \varepsilon_{yy}$ , so the cubic changes to an tetragonal. When a stress along <110> is applied, all of the three strain tensors exist and  $\varepsilon_{yz} = \varepsilon_{xz}$ , so the cubic becomes the orthorhombic.

### 3.4 Strain effects on silicon band structure