## University of Louisville

# ThinkIR: The University of Louisville's Institutional Repository

**Electronic Theses and Dissertations**

5-2018

# Vertical gallium nitride schottky diodes for power switching applications.

Sowmya Kolli University of Louisville

Follow this and additional works at: https://ir.library.louisville.edu/etd

Part of the Electronic Devices and Semiconductor Manufacturing Commons

## **Recommended Citation**

Kolli, Sowmya, "Vertical gallium nitride schottky diodes for power switching applications." (2018). *Electronic Theses and Dissertations*. Paper 2898. https://doi.org/10.18297/etd/2898

This Doctoral Dissertation is brought to you for free and open access by ThinkIR: The University of Louisville's Institutional Repository. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of ThinkIR: The University of Louisville's Institutional Repository. This title appears here courtesy of the author, who has retained all other copyrights. For more information, please contact thinkir@louisville.edu.

# VERTICAL GALLIUM NITRIDE SCHOTTKY DIODES FOR POWER SWITCHING APPLICATIONS

By

Sowmya Kolli B.S., Jawaharlal Nehru Technological University, 2010 MS., University of Louisville, 2012

A Dissertation Submitted to the Faculty of the J.B. Speed School of Engineering of the University of Louisville in Partial Fulfillment of the Requirements for the Degree of

> Doctor of Philosophy In Electrical Engineering

Department of Electrical & Computer Engineering University of Louisville Louisville, KY 40292

May 2018

# VERTICAL GALLIUM NITRIDE SCHOTTKY DIODES FOR POWER SWITCHING APPLICATIONS

By

Sowmya Kolli B.S., Jawaharlal Nehru Technological University, 2010 MS., University of Louisville, 2012

A Dissertation Approved on

December 14, 2017

by the following Dissertation Committee:

Dissertation Director Dr. Bruce W. Alphenaar

Dr. Mahendra K. Sunkara

Dr. Shamus McNamara

Dr. Kevin Walsh

## DEDICATION

This dissertation is dedicated to my parents, grandmother, and brother. I thank my family for the confidence and support they have shown on me throughout my life. This work is also dedicated to my husband, Viraj who has been a constant source of support and encouragement during the challenges of grad school and life.

## ACKNOWLEDGEMENTS

The research included in this dissertation could not have been performed if not for the assistance, and support of many individuals. First and foremost, I would like to express my gratitude to my thesis advisor Dr. Bruce Alphenaar for mentoring me over the course of seven year starting from my Masters through Ph.D. studies. I consider it as a great opportunity to do my doctoral research under his guidance and to learn from his research expertise. Second, I would like to thank Dr. Mahendra Sunkara for being a constant drive to undertake this research in power electronics. It was an amazing experience while working with his group in the initial days of my research which enabled to learn great insights of materials science. I would like to thank Dr. Shamus McNamara, for all the discussions related to research that I had over the years. His ideas and suggestions were helpful in pursuing the device fabrication in right direction. I would like to thank Dr. Kevin Walsh, for providing access to electrical characterization tools in his lab and for taking time in training on various probe stations and microscope.

I would like to thank Conn Center for Renewable Energy Research for providing the funding which allowed me to undertake this research. I would like to thank Curt, Xiaojin and other MNTC staff for familiarizing me with microfabrication processes and clean room routines during my early days. I would like to thank the researchers that I had the pleasure of working with Dr. Srikanth Ravipati from CONN center, Douglas from electrical engineering and Prabhu from APIQ LLC for their assistance with my work. Last but not least, I would like to acknowledge my current lab mates Kasun, Austin, and George. The group has been a source of friendships as well as good advice and collaboration. I would also like to thank other graduate students in Shumaker research building for working together late nights before deadlines. Over the course of my stay at the University of Louisville, I had the opportunity to work with students, researchers, and staff from CONN center and Electrical engineering and I thank all of them for their support and help.

## ABSTRACT

# VERTICAL GALLIUM NITRIDE SCHOTTKY DIODES FOR POWER SWITCHING APPLICATIONS

Sowmya Kolli

#### December 14, 2017

Gallium nitride (GaN) has enormous potential for use in devices operating at high power, frequency and temperature. Its wide band gap, high critical electric field and favorable carrier properties lead to lower switching losses and conduction losses in power electronic devices. However, most GaN rectifiers reported to date exhibit an ON-resistance (Ron) versus breakdown voltage much below theoretical predictions. Heteroepitaxial growth of GaN on substrates such as SiC, Si, and sapphire suffer from a high density of threading dislocations defects due to the mismatch in lattice constants and thermal expansion coefficients. Vertical devices, in which a bulk GaN substrate is used, have much lower defect densities. However, field crowding at the periphery of the rectifying contact remains a problem and results in avalanche break down at much lower voltages than the theoretical maximum. This work will describe the design, simulation and fabrication of a novel wraparound field plate termination structure for high voltage Schottky diodes. Simulations show that the wrap around structure has an improved electric field distribution leading to higher breakdown voltages than conventional diode designs.

The fabrication process was first developed using low-cost commercially grown HVPE GaN on sapphire substrates. This is the first work in the field of GaN based devices at University of Louisville, so all fabrication processes, including ICP/RIE based dry etch, ohmic metal contact deposition and dielectric deposition steps, were developed and optimized. Current-voltage (I-V) measurements were used to extract on-resistance and break down voltage and these results were compared to simulation. Experimentally found breakdown values differed from the theoretical predictions. Device failure analysis based on I-V characterization showed the presence of additional current conduction paths along the SiNx and the defective HVPE films. To prevent these leakage currents a less defective MOCVD film grown on Ammono bulk GaN was used to fabricate the wrap-around diode.

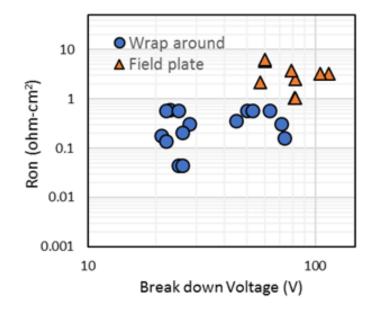

Planar GaN diodes, and diodes with standard field plate and our novel wraparound field plate were built and tested. Interestingly, planar diodes showed higher performance compared to standard field plate and wraparound field plate designs, contradicting to simulation results. Also, the diodes with a standard and a wraparound field plate structures showed higher leakage currents in both forward and reverse bias. To trace out the source of leakage currents, device failure analysis based on I-V measurements were carried out after each fabrication step of the diode. In this process, initially planar diodes were tested with a Schottky and ohmic contacts formed on top and on the back side of the wafer. Then, diodes with mesa are built and tested. The diodes with mesa showed an improvement in breakdown values, with the highest breakdown voltage of 421V and on resistance of 3 mOhms-cm<sup>2</sup>. Also, the experimentally determined breakdown voltages in mesa diodes were found to match with simulation results. Proving that modification in device geometry results in uniform field distribution at the edges and improving the breakdown. Then, a thick SiNx was deposited on mesa diodes using PECVD. The I-V after dielectric deposition showed almost 3 orders higher currents in both forward and reverse bias currents. A similar increase in leakage currents was observed in earlier diodes made on HVPE films. This indicates that PECVD deposited SiNx is modifying the GaN surface and is resulting in additional currents along the GaN and SiNx interface. To overcome these passive currents, a higher K dielectric material was deposited using ALD prior to SiNx. The new bilayer passivation was successful in preventing the leakage currents and resulted in improved breakdown voltages. However, the breakdown values were still below the theoretical predictions and also lower than the diode with a standalone mesa and no additional dielectric layer. Indicating that improvement produced by the device geometry modification is negated by dielectric deposition.

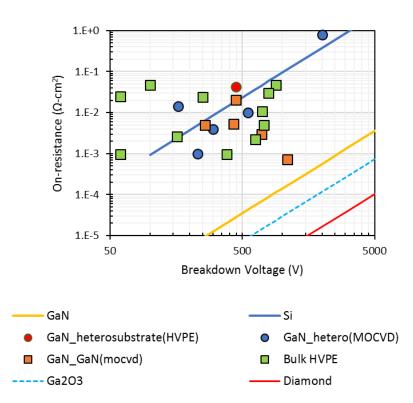

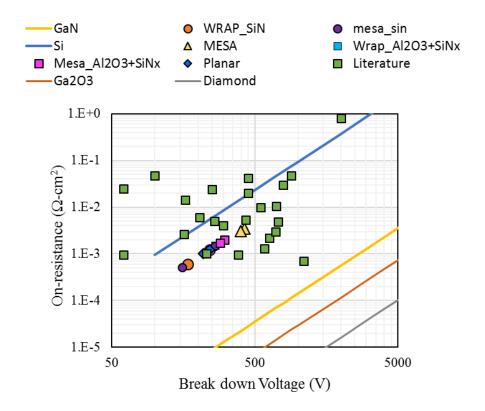

Further, we compared some of our diodes with best breakdown characteristics to the literature. We found that with the given material quality and drift layer thickness, we were able to achieve higher breakdown compared to most of the devices reported in the literature. However, there are few diodes with better on resistance and breakdown values compared to ours. As these diodes used almost 60 to 100 times thicker films compared to ours.

We were able to make Schottky diodes with relatively high breakdown voltages. However, to utilize the effect of wraparound field plate to its fullest potential, there is a need to develop an alternative dielectric material and deposition technique in future.

# TABLE OF CONTENTS

| ABSTRACT                                                  | vi |

|-----------------------------------------------------------|----|

| CHAPTER 1 INTRODUCTION                                    | 1  |

| 1.1 ENERGY CHALLENGE                                      | 1  |

| 1.2 WIDE BANDGAP MATERIAL PROPERTIES AND THEIR ADVANTAGES | 4  |

| 1.3 GROWTH TECHNIQUES                                     | 9  |

| 1.4 MOTIVATION                                            | 13 |

| 1.5 OUTLINE                                               | 17 |

| CHAPTER 2 LITERATURE REVIEW AND BACKGROUND                | 19 |

| 2.1 INTRODUCTION                                          | 19 |

| 2.2 SCHOTTKY RECTIFIER                                    | 20 |

| 2.3 MATERIAL SYSTEMS                                      | 25 |

| 2.4 LITERATURE REVIEW                                     | 29 |

| CHAPTER 3 SIMULATIONS                                     | 40 |

| 3.1 INTRODUCTION                                          | 40 |

| 3.2 SIMULATION                                            | 41 |

| 3.3 CONCLUSION                                                    | 52  |

|-------------------------------------------------------------------|-----|

| CHAPTER 4 LATERAL GAN SCHOTTKY DIODES ON HVPE GROWN FILM SAPPHIRE |     |

| 4.3 DEVICE FABRICATION                                            | 58  |

| 4.4 ELECTRICAL MEASUREMENTS                                       | 61  |

| 4.5 RESULTS AND DISCUSSION                                        | 62  |

| CHAPTER 5 VERTICAL SCHOTTKY DIODES ON BULK GAN SUBSTRATES         | 72  |

| 5.1 INTRODUCTION                                                  | 72  |

| 5.2 MATERIAL CHARACTERIZATION                                     | 72  |

| 5.3 DEVICE FABRICATION                                            | 73  |

| 5.4 ELECTRICAL MEASUREMENTS                                       | 77  |

| 5.5 RESULTS AND DISCUSSION                                        | 78  |

| CHAPTER 6 CONCLUSIONS                                             | 97  |

| CHAPTER 7 FUTURE WORK                                             | 102 |

| REFERENCE                                                         | 105 |

| APPENDIX: A                                                       | 112 |

| CURRICULUM VITAE                                                  | 131 |

# LIST OF FIGURES

| Figure 1-1: Demand for electricity in residential, commercial, industrial and transportation sector  |

|------------------------------------------------------------------------------------------------------|

| (source: US Energy Information Administration)2                                                      |

| Figure 1-2: Wide bandgap semiconductor properties and high-power applications                        |

| Figure 1-3: Bandgap Vs bond length for different semiconductors [11]5                                |

| Figure 1-4: Electric field distribution in reverse bias for a vertical Schottky diode                |

| Figure 1-5: Field distribution at the breakdown for Si and wide bandgap (GaN) based Schottky         |

| diode7                                                                                               |

| Figure 1-6: Ron Vs Breakdown voltage limit for Si, SiC and GaN                                       |

| Figure 1-7: HVPE growth of GaN[22, 23]10                                                             |

| Figure 1-8: MOCVD reactor set up for GaN growth11                                                    |

| Figure 1-9: GaN bulk crystals obtained by Ammono thermal method [30] 12                              |

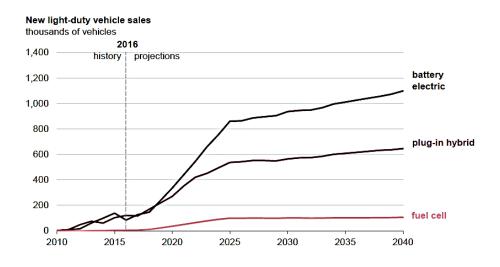

| Figure 1-10:Light-duty vehicle sales from 2010 to 2040 (source: US Energy Information                |

| Administration)14                                                                                    |

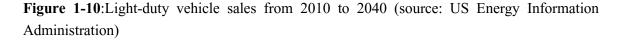

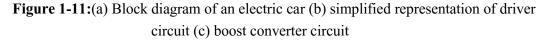

| Figure 1-11:(a) Block diagram of an electric car (b) simplified representation of driver circuit (c) |

| boost converter circuit                                                                              |

| Figure 2-1: Energy band diagram for a metal and semiconductor (a) in isolation (b) after making      |

| and electrical connection [96]20                                                                     |

| Figure 2-2: Break down Vs. drift region doping concentration of GaN [11]25                           |

| Figure 2-3: Current flow in vertical device and in lateral device                                    |

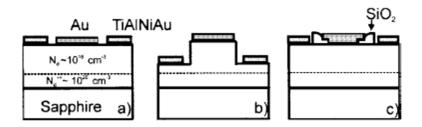

| Figure 2-4: Schematic of GaN Schottky rectifier built from HVPE grown layers on sapphire. (a)        |

| lateral diode (b) mesa diode (c) lateral diode with a field plate extending over SiO2[47].30         |

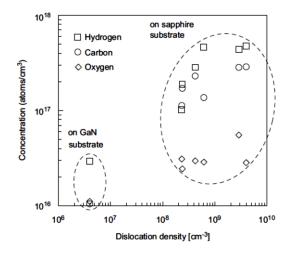

| Figure 2-5: Schematic of Schottky rectifier fabricated on free-standing GaN with field               |

| termination [50]                                                                                     |

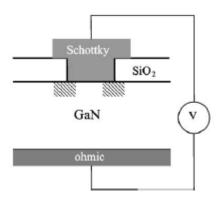

| Figure 2-6: Dependence of impurity concentration on the defect density[51]                           |

|------------------------------------------------------------------------------------------------------|

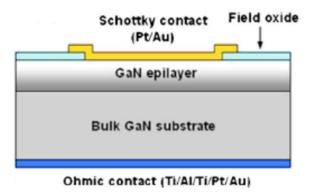

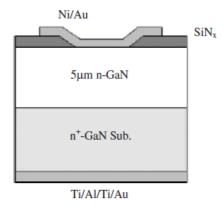

| Figure 2-7: Schematic of vertical Schottky rectifier fabricated on bulk GaN substrate[52]34          |

| Figure 2-8: Schottky rectifier structure with the field plate reported by Saitoh et al.[53]          |

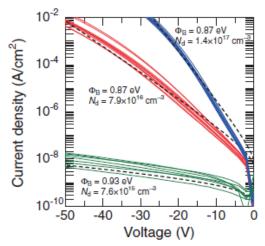

| Figure 2-9: Reverse I-V characteristics of GaN Schottky barrier diodes with different donor          |

| concentration of 7.6 x $10^{15}$ , 7.9 x $10^{16}$ and 1.4 x $10^{17}$ cm <sup>-3</sup> [55]36       |

| Figure 2-10: On resistance Vs. Breakdown voltages for Schottky rectifiers reported in the            |

| literature                                                                                           |

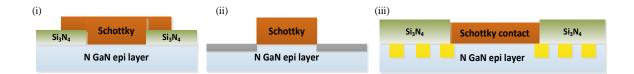

| Figure 2-11: Common field termination techniques (i) field plate design (ii) damage implant(iii)     |

| guard-ring using p implants                                                                          |

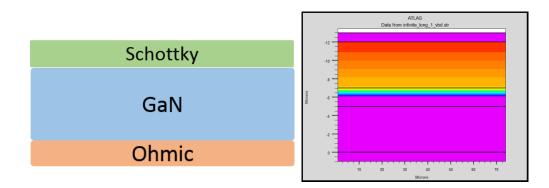

| Figure 3-1: Ideal diode with infinitely long contacts(left) Field distribution during the breakdown  |

| of ideal diode at 1600V (right)43                                                                    |

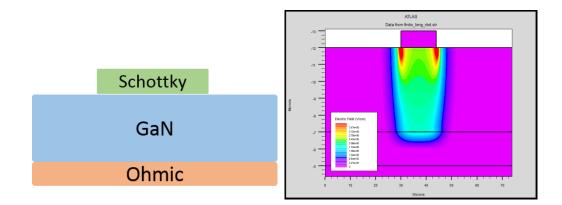

| Figure 3-2: Field distribution in a real diode at the breakdown voltage of 500V44                    |

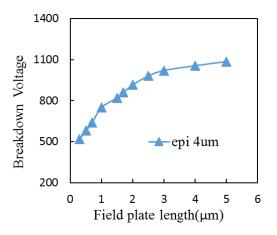

| Figure 3-3: Breakdown Vs. Field plate length for a standard filed plate geometry                     |

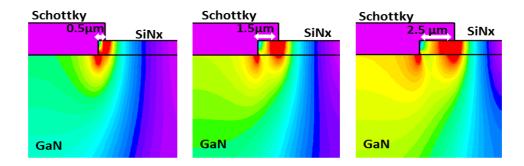

| Figure 3-4: Field distribution at different field plate length                                       |

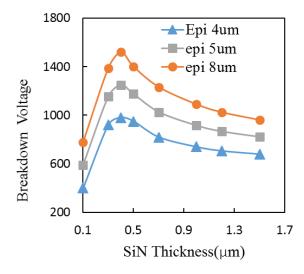

| Figure 3-5: Breakdown Vs. SiNx thickness                                                             |

| Figure 3-6: Wraparound architectures                                                                 |

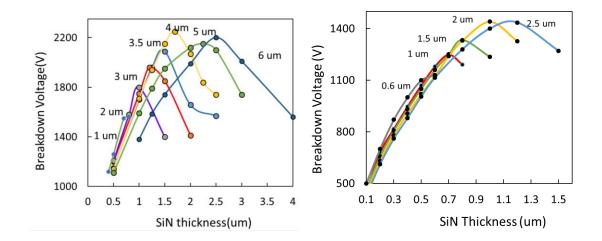

| Figure 3-7: Breakdown voltage Vs. Dielectric thickness for different mesa depth for an 8µm           |

| epilayer (left) 5µm epilayer (right)                                                                 |

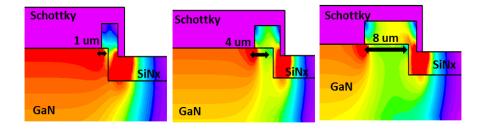

| Figure 3-8: Field distribution for diodes with different SiNx neck length                            |

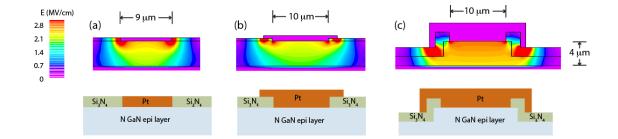

| Figure 3-9: Field distribution in basic diode (a)without field plate, (b) with field plate, (c) with |

| wrap around field plate                                                                              |

| Figure 3-10: forward bias for wrap around(red) and standard field plate design(yellow)               |

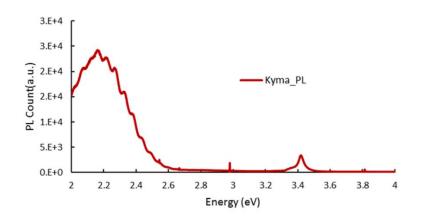

| Figure 4-1: PL spectrum for HVPE grown GaN film on Sapphire                                          |

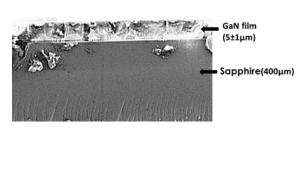

| Figure 4-2: cross-sectional view of GaN on Sapphire                                                  |

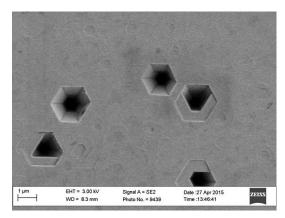

| Figure 4-3: Selectively etching of defects using phosphoric acid at 110C                             |

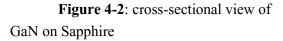

| Figure 4-4: Rocking curve for HVPE GaN on sapphire from (0002) reflection                            |

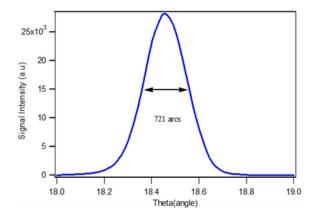

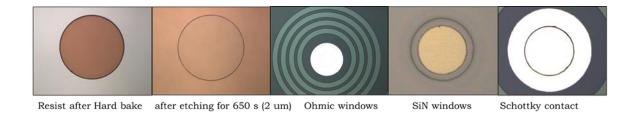

| Figure 4-5: Process flow for lateral wrap around field plate                                       |

|----------------------------------------------------------------------------------------------------|

| Figure 4-6: Microscopic images for each step involved in the device fabrication                    |

| Figure 4-7: Process flow for lateral field plate diode                                             |

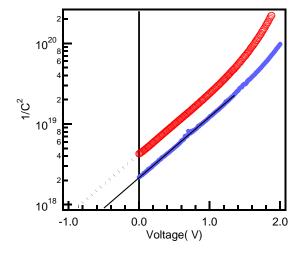

| Figure 4-8: $1/C^2$ - V for HVPE grown on sapphire at room temperature                             |

| Figure 4-9: Ron versus breakdown for diodes with field plate and wraparound                        |

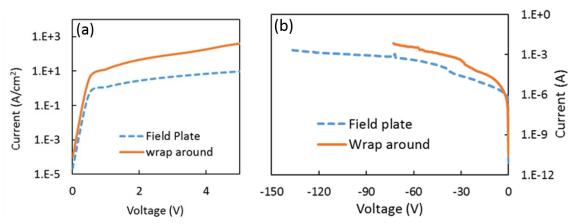

| Figure 4-10: I-V for 25µm radius diode with standard field plate (dash line) and wrap around       |

| structure (solid line) (a) forward characteristics (b) reverse characteristics                     |

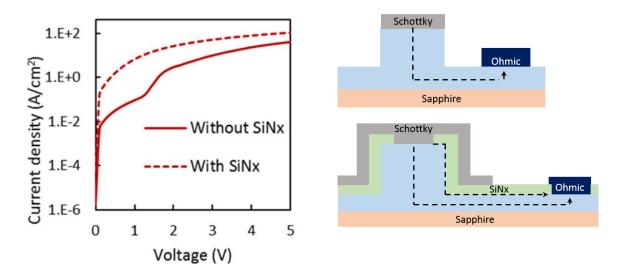

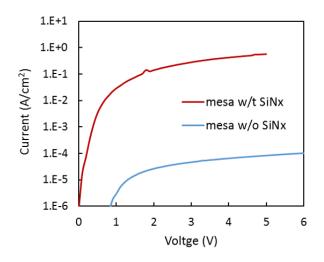

| Figure 4-11: I-V for mesa with and without PECVD SiNx(left) diode schematic showing the            |

| current paths with and without SiNx(right)65                                                       |

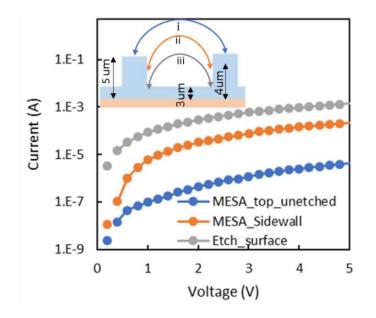

| Figure 4-12: I-V measured by placing the probes on top of mesa surface (unetched), sidewall and    |

| the etched surface                                                                                 |

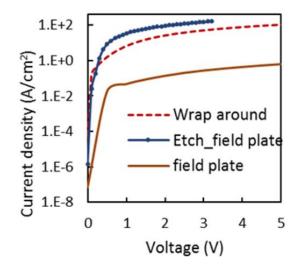

| Figure 4-13: Forward characteristics for a wraparound, standard field plate and etched field plate |

|                                                                                                    |

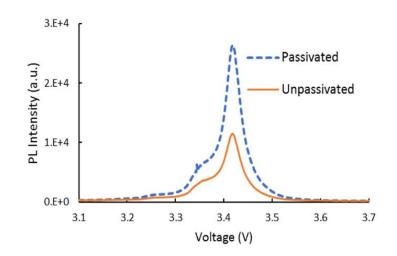

| Figure 4-14: PL for passivated and un-passivated samples at room temperature                       |

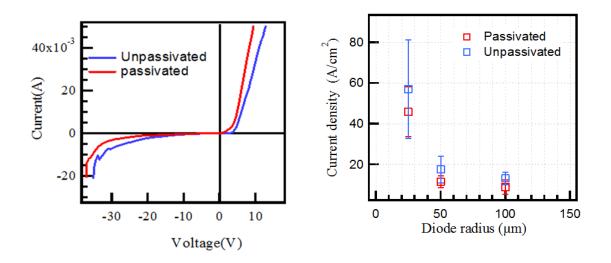

| Figure 4-15: I-V for a 50um radius diode passivated (red) Vs. un-passivated(blue)69                |

| Figure 4-16: Average leakage current density Versus diode radius for passivated and                |

| Unpassivated diodes                                                                                |

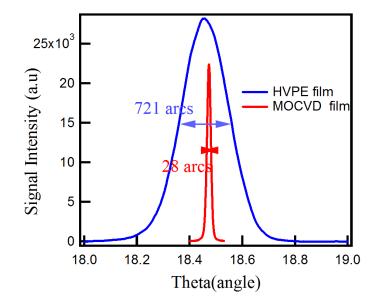

| Figure 5-1: XRD rocking curve for MOCVD grown GaN film bulk Ammono thermal(red) and                |

| HVPE grown on sapphire (blue)73                                                                    |

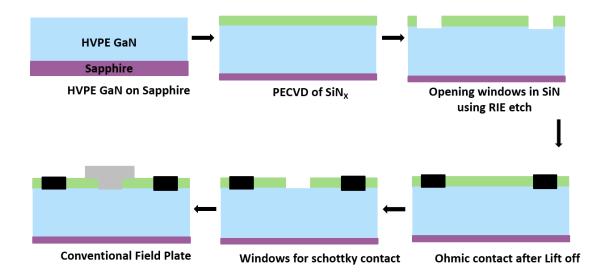

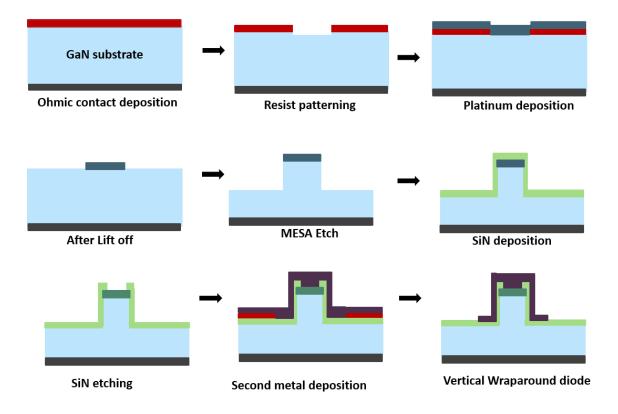

| Figure 5-2: Process flow for vertical wraparound diode74                                           |

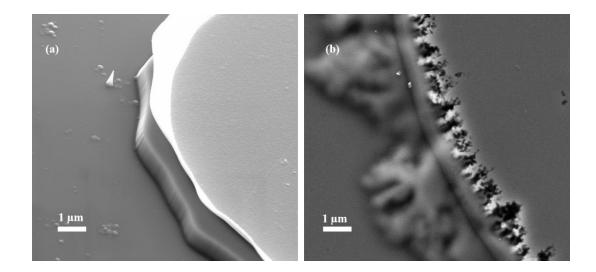

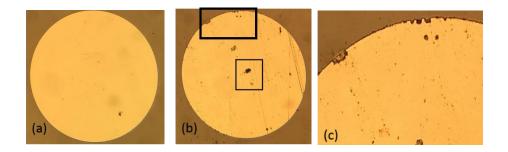

| Figure 5-3: Mesa side wall surface after dry etching in Cl2/BCl3/Ar (a) metal mask (b)             |

| photoresist mask                                                                                   |

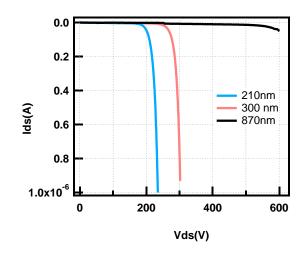

| Figure 5-4: Breakdown characterization for SiNx layer for different thickness77                    |

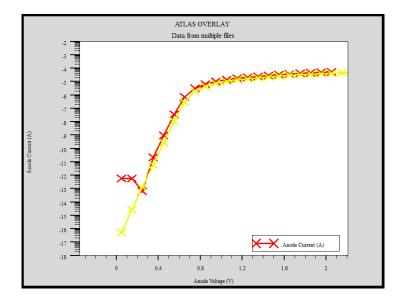

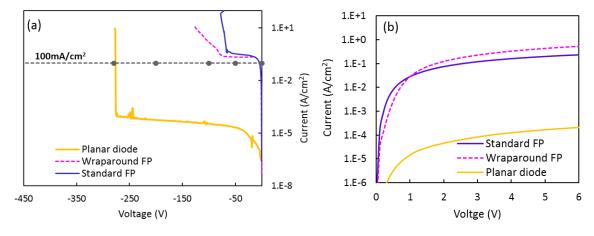

| Figure 5-5:I-V for a standard field plate, wraparound and planar diode (a) reverse (b) forward     |

| bias                                                                                               |

|                                                                                                    |

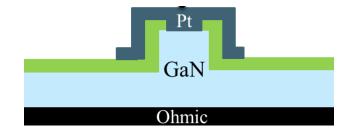

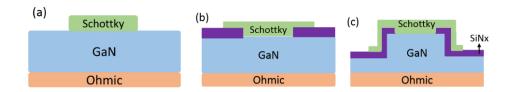

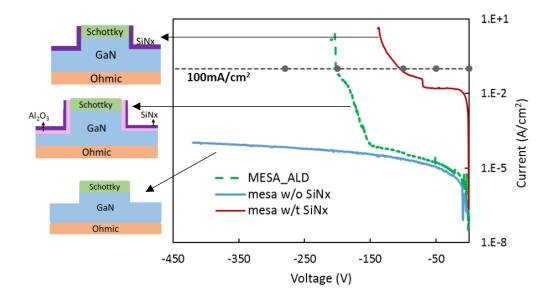

Figure 5-6:Schematic for (a) planar diode (b) standard field plate (c) wraparound field plate..78

| Figure 5-7: Microscope images of the diode(a) before applying bias (b) at the breakdown with       |

|----------------------------------------------------------------------------------------------------|

| the black spots appearing on the edges and on the diode (square regions). (c) Zoomed in            |

| view of the breakdown spots at the edges                                                           |

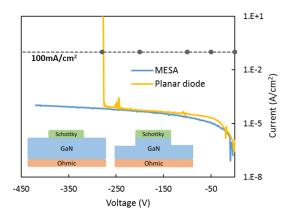

| Figure 5-8: Reverse bias I-V for a planar diode and a mesa diode. Blue horizontal dotted line      |

| indicates the current density at the breakdown. Insite showing a planar and mesa diode80           |

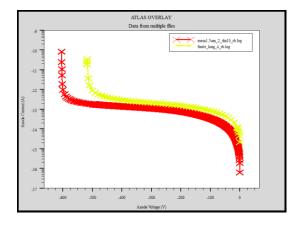

| Figure 5-9: I-V comparing the breakdown voltage of a mesa diode(red) and a planar                  |

| diode(yellow)                                                                                      |

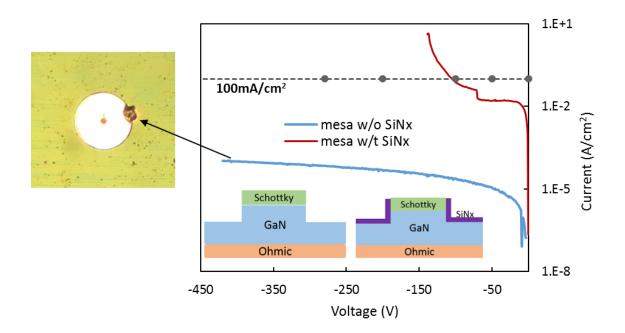

| Figure 5-10: Reverse bias characteristics for a mesa diode with(blue) and without(red) SiNx        |

| layer. Dotted horizontal trace corresponds to current density at which diodes breakdown is         |

| defined83                                                                                          |

| Figure 5-11: Forward I-V for a mesa diode at room temperature, with and without SiNx layer84       |

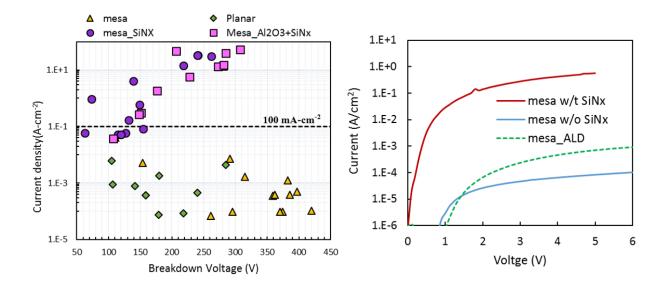

| Figure 5-12: Comparing reverse bias I-V for mesa diode with different surface passivation87        |

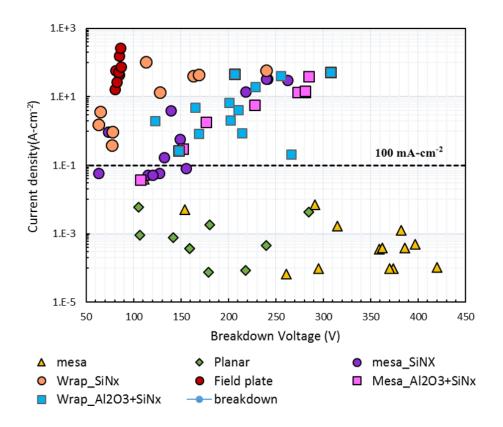

| Figure 5-13: Reverse bias current density Vs. breakdown voltages for mesa diodes with different    |

| passivation and a planar diode                                                                     |

| Figure 5-14: Comparing forward bias I-V for mesa diode with different surface passivation88        |

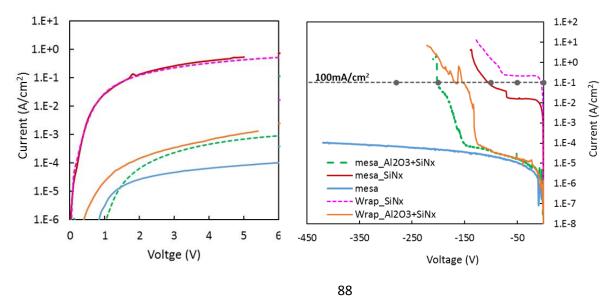

| Figure 5-15: I-V characteristics of a mesa and a wraparound diode with SiNx and with Al2O3 &       |

| SiNx                                                                                               |

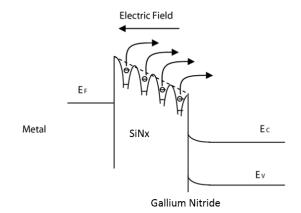

| Figure 5-16:Tunneling currents across the gate, SiNx and GaN interface                             |

| Figure 5-17: Current density for all diodes and corresponding breakdown values                     |

| Figure 5-18: On resistance Vs breakdown voltage of the diodes in the literature and for the diodes |

| from the current work                                                                              |

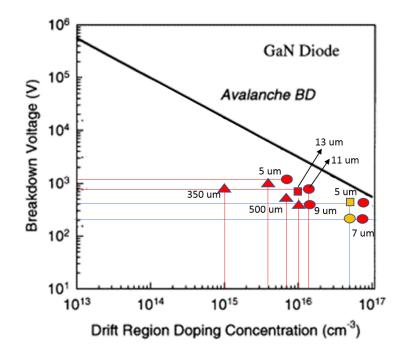

| Figure 5-19: Breakdown voltage Vs. doping concentration for diodes reported in literature(red)     |

| and the diodes from this work(yellow)                                                              |

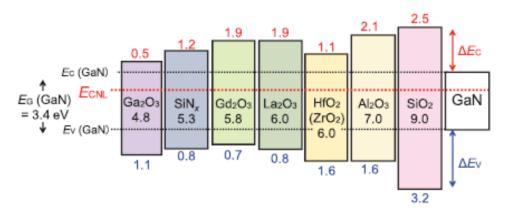

| Figure 6-1: Dielectric materials and the energy gaps between their conduction band with respect    |

| to GaN [95]103                                                                                     |

## LIST OF TABLES

| Table 1-1: Material parameters for Si, SiC[7],GaN[8], Ga2O3 and Diamond[9]4                      |

|--------------------------------------------------------------------------------------------------|

| Table 1-2: Summary of GaN growth techniques    13                                                |

| Table 2-1: Drift layer thickness, doping concentration and breakdown voltages of the diodes      |

| built on films grown by HVPE, MBE, MOCVD (nominal buffer) and MOCVD (modified                    |

| buffer)[48]31                                                                                    |

| Table 3-1 Material parameters used in GaN Schottky diode simulation[62-64]                       |

| Table 3-2: simulated breakdown values for different field plate diodes                           |

| Table 5-1: Electric field strength for PECVD deposited SiNx layers of different thicknesses77    |

| Table 5-2: Dielectric materials and deposition type used in literature(left) currently available |

| resources(right)                                                                                 |

| Table 5-3 : MOCVD grown epilayer and Ammono bulk substrate properties provided by the            |

| manufacturing company                                                                            |

## CHAPTER 1 INTRODUCTION

## 1.1 Energy Challenge

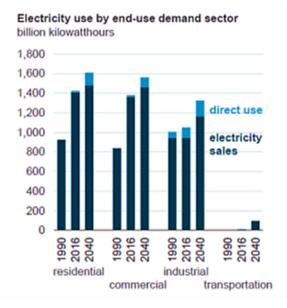

In the modern-day energy is generated from a variety of sources such as solar energy, wind energy, fossil fuels, hydel energy and nuclear energy. Generated energy is stored, transported, converted and consumed. The mode of energy consumed can be classified as electricity, heat, chemical, and other forms. Among these, energy consumed in the form of electricity is increasing and is expected to grow more in the future. Figure 1-1 shows the end use of electricity in sectors including residential, commercial, industrial and transportation from 1990 to 2040 in United states.

**Figure 1-1**: Demand for electricity in residential, commercial, industrial and transportation sector (source: US Energy Information Administration)

In 2015, the U.S. Energy Information Administration (EIA) estimated a loss of about 6.31% of electricity in the process of transmission and distribution of electricity. From percentage viewpoint this might appear to be relatively low, but the total estimated electricity loss was 10.8 quads. With the increased need of electricity there is a demand for the efficient and reliable management of electrical energy, and power electronics is a technological domain that deals with the electrical energy conversion by switching for dynamic power management[1]. These power conversions can range from milli watts to thousands of megawatts. Power electronics translate the properties such as voltage, current and frequency to required specifications according to the intended application. These conversions are found in solar inverters[2], automotive industry[3], robotics, and power supplies for electronics[4]. The main principle of power conversion is digital switching. For ideal power electronic switches

(i) The voltage drop in the forward bias (on state) should be zero, i.e. no conducting losses.

(ii) The transition from on state to off state should be instantaneous with no switching losses.

(iii) Leakage current in reverse bias (off state) should be zero, i.e., infinite off resistance.

However, in every conversion process, the power losses[5] are inevitable due to switching. Thus, reduction of this energy loss during power conversions is indispensable for efficient management of electric power in the grid.

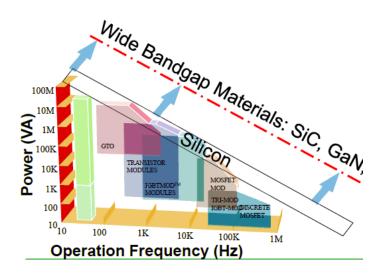

Silicon(Si) has served the power electronics industry exceptionally well, in the form of MOSFET, and various adaptations such as IGBT, BJT, and diodes for over 45 years. However, to meet the demand for electricity in future, and to efficiently reduce the losses during modulation of electric power, requires the development of new materials that can operate at higher frequency to shrink the size of passive components and reduce the overall copper loss and higher operating temperatures to cut the additional energy required by heat sinks.

Figure 1-2: Widebandgap material operation range in terms of frequency and power

Also Silicon-based devices have reached the theoretical performance limit set by fundamental material properties and there is considerable attention in the development of wide bandgap materials such as Silicon Carbide (SiC), Gallium Nitride (GaN),Gallium Oxide(Ga<sub>2</sub>O<sub>3</sub>) and Dimond[6]. The wide bandgap semiconductors because of their material properties as listed in table 1-1, such as bandgap, critical electric field, and higher drift velocity are predicted to have low loss and improved efficiency compared to Si devices.

| Semiconductor<br>material                    | Units               | Silicon | SiC  | GaN  | Ga <sub>2</sub> O <sub>3</sub> | Diamond |

|----------------------------------------------|---------------------|---------|------|------|--------------------------------|---------|

| Bandgap                                      | Ev                  | 1.12    | 3.26 | 3.45 | 4.5-4.9                        | 5.5     |

| Dielectric constant( $\varepsilon_s$ )       |                     | 11.8    | 9.7  | 10.4 | 10                             | 5.5     |

| Mobility $(\mu_n)$                           | cm <sup>2</sup> /Vs | 1400    | 950  | 1245 | 300                            | 2000    |

| Critical Electric field<br>(E <sub>c</sub> ) | MV/cm               | .25     | 2.2  | 3.5  | 8                              | 10      |

Table 1-1: Material parameters for Si, SiC[7],GaN[8], Ga2O3 and Diamond[9]

#### 1.2 Wide bandgap material properties and their advantages

## **1.2. (a) Chemical stability**

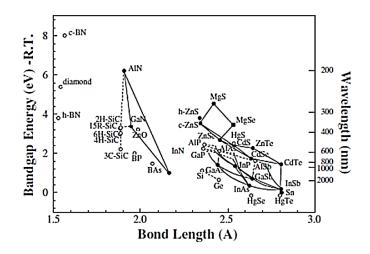

Group III nitrides and SiC are covalent bond crystals composed of light elements of the second period of the periodic table, which have characteristics of small bond length between the constituent atoms and wide bandgap energy in comparison with Si and GaAs[10]. Figure 1-3 illustrates the relationship between bond length and bandgap for various semiconductor materials. SiC and GaN are in a different domain from conventional elemental and compound semiconductors. These materials have a lower bond length which means that the bonding energy between the constituent atoms is strong and as a result, the chemical stability of WBG materials is extremely high.

Figure 1-3: Bandgap Vs bond length for different semiconductors [11]

## 1.2 (b) Higher operating temperatures

The wider bandgap energies in these materials result in lower intrinsic carrier concentration compared to Si or GaAs. Also, due to wide bandgaps, these semiconductor materials can withstand higher operating temperatures (250°C-300°C) before undergoing thermal runaway. On the other hand, Si devices can only operate at temperatures lower than 100°C due to their lower bandgap and higher intrinsic carrier concentration. Thus, the lower intrinsic carrier concentration and wider bandgap make WBG materials attractive for higher temperature function at an ambient temperature >150°C without additional cooling requirements, potentially reducing the volume, weight, and cost of the converter.

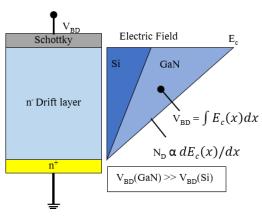

## 1.2 (c) Higher blocking voltages

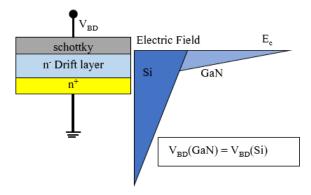

In reverse bias, the electric field in the drift layer is illustrated in figure 1-3. An avalanche breakdown occurs when the electric field at the junction reaches the critical electric field of the

material. As the Critical electric field of WBG materials is ten times higher than Si. This enables devices based on SiC and GaN to block higher voltages for a given drift region width.

$$V_{BD} = \frac{E_c W_d}{2} \quad (1-1)$$

W<sub>d</sub>: Drift layer width Ec: Critical electric field

Figure 1-4: Electric field distribution in reverse bias for a vertical Schottky diode

## 1.2 (d) Lower On-resistance

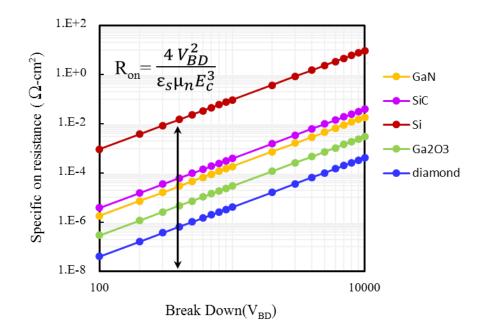

In the forward bias the potential drop across the drift layer is defined as the specific resistance and is expressed as a function of drift layer width and carrier concentration( $N_D$ ).  $N_D$  as mentioned earlier is directly proportional to the critical electric field (refer Eq (1-3)) of the material. Since, WBG materials have higher  $E_C$ , compared to Si, WBG drift layers can be doped more than ten times higher, and thus the drift layer width can be 1/10 times thinner than Si assuming same breakdown voltage as illustrated in figure 1-5. Substituting,  $V_{BD}$  and  $N_D$  into Eq (1-2), gives  $R_{ON}$  in terms of  $E_C$ ,  $\mu_n$  and  $V_{BD}$ . From Eq 1-4, it is apparent that material with high Ec and mobility will result in lower Ron for similar breakdown values. A plot of on-resistance

and breakdown, are the two critical parameters for evaluating any material system as a switch. As shown in figure 1-6, for a given breakdown voltage WBG materials offer lower  $R_{ON}$  there by decreasing the conduction loss in a switch ( $I^2R_{ON}$ )

$$R_{ON} = \frac{W_D}{q u_n N_D}$$

(1-2)

$$N_{\rm D} = \left(\frac{\varepsilon_{\rm s}}{q}\right) \left(\frac{E_{\rm c}}{W_{\rm D}}\right) \qquad (1-3)$$

$$R_{ON} = \frac{4V_{\rm BD}^2}{\varepsilon_{\rm S} u_{\rm n} E_{\rm C}^3} \tag{1-4}$$

- q: Electron charge

- $\mu_n$ : Electron mobility

- $\varepsilon_s$ : Specific dielectric constant

Figure 1-5: Field distribution at the breakdown for Si and wide bandgap (GaN) based Schottky diode

Figure 1-6: Ron Vs Breakdown voltage limit for Si, SiC, GaN, Ga2O3 and Diamond.

Thus, the characteristics of wide bandgap materials such as, high critical electric field, high-temperature stability and high saturation drift velocity equate to a low loss, requiring smaller heats sinks, reduced cooling costs, high-efficiency power conversion and theoretically make these materials a potential substitute for Si to develop high power devices. Among the SiC and GaN material systems, SiC is more matured[12-15], and SiC-based devices such as Schottky diodes, MOSFETs are commercially produced by manufacturing companies such as Rohm, Infineon, CREE, and others. GaN with a higher bandgap, and higher electron mobility than SiC, is at a nascent phase in the field of power electronics. The commercialization of GaN-based power devices is slowed down mainly due to lack of availability of GaN bulk substrates.

Typically, GaN is grown either on sapphire or SiC. When grown on SiC, the material itself is more expensive and defective than SiC. Interestingly, GaN grown on heterosubstrates

with a high density of defects are widely used for LEDs development[16, 17]. In fact, GaN along with its ternary alloys based LEDs can cover a wide spectral range from green to ultraviolet. However, for power devices, these defects can drastically impair the efficiencies. Lately, GaN growth is optimized, and various techniques were instigated by different groups at universities and industries to realize bulk GaN substrates and high-quality GaN films for high power applications.

The following section describes various growth methods reported in the literature along with the advantages and disadvantages of each technique.

## **1.3 Growth techniques**

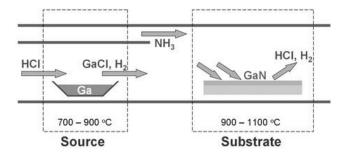

## (a) Hydride vapor phase epitaxy(HVPE)

HVPE is one of the most commonly used epitaxial growth process, in which HCl reacts with liquid Gallium to form GaCl. Subsequently GaCl along with NH<sub>3</sub> are carried to process chamber (typically a quartz furnace) using H<sub>2</sub> or N<sub>2</sub> or argon gas to form GaN. Figure 1-8, illustrates the HVPE growth steps. This technique results in higher growth rate compared to any other methods on the order of 200 - 300  $\mu$ mh<sup>-1</sup>, on relatively large (2 -in.) substrate. However, films grown using HVPE technique suffer from higher threading dislocation density (TDD) on the order of 10<sup>9</sup>cm<sup>-2</sup> when grown on heterosubstrates[18]. For instance, the lattice mismatch between GaN and substrates such as Si, SiC, and sapphire are reported to be 17%,3.3%, and 13% respectively[19]. Additionally, HVPE layers are rough and suffer from high strain resulting in bowing[20]and cracking at the GaN/Substrate interface[21].

Figure 1-7: HVPE growth of GaN[22, 23]

**HVPE Bulk substrates**: To reduce the threading dislocations, thicker GaN films are grown on sapphire, as the threading dislocation density (TDD) is higher at the interface and the defects propagate along the direction of the growth for several microns. For the layers on the order of 350 - 500 um thick, the number of defect lines that extend to the surface tends to decrease. Further, GaN layers are peeled off from substrates resulting in a bulk substrate lower TDD values of 10<sup>6</sup>cm<sup>-2</sup>[24]. But, even after the separation of the freestanding GaN layer from heterosubstrates, GaN wafers are typically bowed.

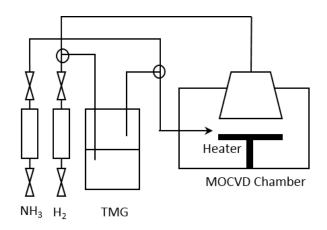

## (b) Metal organic chemical vapor deposition (MOCVD)

After HVPE, MOCVD is the most widely implemented method to grow high-quality GaN films on heterosubstrates. MOCVD is a two-step process, involving in (i) transportation of metalorganic and nitrogen precursors to the process chamber and then (ii) reaction on the surface of the heated substrate. Trimethylgallium (TMGa) and NH<sub>3</sub> are typically used sources for Ga, and N. TMGa is initially vaporized by flowing hydrogen gas through the bubbler and is then mixed with NH3 in the main channel. The two precursors are then flowed in parallel into the chamber, to decompose and form GaN on the heated substrate. Also, a secondary gas is flowed perpendicular to the substrate to maintain the reactants closer to the substrate (shown in figure 1-9). Further, using a low temperature grown buffer layer[25], the films produced by MOCVD have resulted in substantially lower TDD on the order of 10<sup>5</sup> cm<sup>-2</sup> even when grown on heterosubstrates.

Figure 1-8: MOCVD reactor set up for GaN growth

Although the MOCVD technique can produce high-quality films[26], the growth rate of this method is very low on the order of 1-2  $\mu$ m/h only.

#### (c) Ammono thermal

Both the growth techniques discussed above completely rely on heterosubstrates such as silicon carbide and sapphire due to lack of freestanding and high-quality GaN substrates. Due to the thermodynamic limitation of GaN, e.g., decomposition at 877°C under atmospheric conditions

[27], it cannot be grown from the stoichiometric melt without extreme pressure and temperature of > 6 GPa at  $2220^{\circ}$ C[28]. Hence, only vapor phase and solution techniques are appropriate to produce group-III nitride crystals in an economic way. More recently, however, the ammonothermal growth of GaN has emerged as a powerful technique for the mass-production of large size GaN crystals [29].

Figure 1-9: GaN bulk crystals obtained by Ammono thermal method [30]

The ammonothermal technique belongs to the wide family of solvothermal techniques, employing a polar solvent of inorganic or organic nature under subcritical or even supercritical conditions to dissolve and re-crystallize a polar material. The process to grow GaN crystals uses a solvent comprised of supercritical ammonia with added mineralizers to grow GaN via recrystallization at seed crystals[31]. Ammonothermal growth is a bulk process that does not use non-native starting substrates. This method has yielded the lowest defect density of  $5 \times 10^3$  cm<sup>-2</sup> in a 1-in. wafer. Following table summarizes all the growth techniques

| Growth Technique                                   | Advantages                                                  | Disadvantages                                              |

|----------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|

| Hydride Vapor Phase epitaxy<br>(HVPE)              | High growth rate $(200 - 300 \ \mu mh^{-1})$                | High defect density<br>(10 <sup>9</sup> cm <sup>-2</sup> ) |

| Metal organic chemical vapor<br>deposition (MOCVD) | Low defect densities<br>(10 <sup>5</sup> cm <sup>-2</sup> ) | Low growth rate $(1-2 \ \mu mh^{-1})$                      |

| Bulk Hydride Vapor Phase<br>epitaxy                | High growth rate $(200 - 300 \ \mu mh^{-1})$                | Cracking at the<br>interface and bowing<br>of the wafer    |

| Ammono thermal                                     | Low defect density<br>(5x10 <sup>3</sup> cm <sup>-2</sup> ) | Long growth time                                           |

**Table 1-2:** Summary of GaN growth techniques

## 1.4 Motivation

The recent development in the bulk substrate technology has boosted the prospects of GaN devices into power arena, beyond the Light industry. Particularly, the expanding automotive industry and the rising prominence of electric vehicles in the global automotive sector is a crucial driver for the GaN power devices market in the coming years[32]. According to US Energy information administration, a rise of 6 and 4% in battery electric and plug in hybrid vehicle sales is predicted in next 20 years.

To understand the role of GaN in battery electric vehicles better, take the example of an electric car. Figure 1-12(a) shows the simple block diagram comprising of various units such as HV battery, boost converter, inverter, electric motor, accessory load DC-DC converter and electric accessory load. Consider the case of high voltage battery connected to a boost converter followed by inverter and then connected to electric motor that generates the torque to drive the vehicle as shown in figure 1-12(b). A battery provides a DC voltage in the range of 200V to 400V, whereas the electric motor needs much higher AC voltages to generate magnetic fields, to run the motor. Therefore, the voltage from the battery is typically fed to a boost converter that steps up the voltage to 650V from 200V and is then fed to an inverter circuit that converts DC to AC as required by the load (electric motor).

Fundamentally, booster converter or inverter blocks are made up of several power switches such as insulated gate bipolar junction transistors(IGBT), MOSFETS and passive components such as capacitors and inductors. Figure 1-12(c) shows the electric circuit for a boost converter. Conventional Si switches as discussed earlier in this chapter can operate at temperatures  $\leq 150^{\circ}$ C. However, booster and inverter are located near the electric motor, where temperature typically rise up to 300°C, therefore Si switches need additional heat sinks which make overall system bulkier and adding extra load on motor. There by affecting efficiency of electric motor. Also, as discussed before, Si based devices because of high on-resistance and lower switching speeds decrease the overall power conversion efficiency. Therefore, automotive industry is showing interest in wide bandgap material systems such as SiC and GaN to replace Si based switches in medium operating power ranges (400V-2000V).

Though, there are good prospects for development of GaN-based devices for the automotive industry, high substrate cost, smaller GaN substrate sizes (2" wafers) and yield-related issues are restraining the expansion of GaN power device market. Thus, leaving scope for developing low-cost material systems and novel device designs that can endure in the medium power regime efficiently. Till date, several groups have reported various GaN-based diodes and transistors (will be discussed in the next chapter) with breakdown voltage ranging from 100's to several 1000's. However, most of them seem to have performance lower than the theoretical maximum due to various factors such as quality of the GaN films, device design[33], fabrication process and others[34].

We particularly got motivated to develop novel device designs that can operate in the medium power regime (400V - 2000V). So, we have started off with two terminal Schottky diodes since we are developing GaN-based power devices for the first time.

## 1.5 Outline

In chapter 2, the basic principle of the metal-semiconductor contact is discussed. Followed by a complete background on various types Schottky diodes reported till date is presented. The impact of the factors such as a quality of the drift layers and device geometry on the diode performance are also discussed.

In Chapter 3, our new wraparound field plate architecture is presented to address the field crowding-related issues more efficiently than the conventional geometries. The impact of each geometrical aspect on the wraparound diode is studied, and an optimized structure with the breakdown voltage suitable for automotive applications in the range of 400V to 1600V is developed. The field distribution in various diodes including an ideal diode, a diode with finite Schottky contact length and a standard field plate at breakdown are simulated and compared to wraparound.

Chapter 4 discusses the fabrication and electrical characterization of lateral diodes built from HVPE grown films on sapphire. A standard field plate and a wraparound field plate are tested and compared to simulation results. The impact of surface defects and bulk defects on the diode breakdown voltage are studied. Also, the effect of surface passivation using ammonium sulfide is described.

In chapter 5, vertical diodes built on low defective films grown using MOCVD on Ammono bulk substrate are discussed. Issues related to etch induced defects, parasitic currents across the GaN and dielectric interface that were encountered in lateral diodes are studied systematically by electrical characterization of the diode after each fabrication step. Also, an optimized dry etch process is developed to minimize the surface currents. Further, a bilayer dielectric structure is employed to overcome the issues introduced by PECVD deposited dielectric film.

Chapter 6 and 7 summarizes the challenges in the device fabrication and discusses the future directions in terms of material growth and fabrication processes to realize diodes with higher efficiencies.

# CHAPTER 2 LITERATURE REVIEW AND BACKGROUND

# **2.1 Introduction**

A Schottky rectifier is formed by making an electrically nonlinear contact between a metal and a semiconductor. The Schottky rectifier is a unipolar device attractive for power applications due to its relatively low on-resistance and fast switching speed. Si-based Schottky diodes have been used extensively in power supply circuits with low operating voltages. However, for automotive applications, devices with higher operating temperatures, voltages > 400V and higher switching speeds are required. In the case of Si, commercial Si Schottky diodes can operate at voltages <100V and the novel device geometry that uses charge-coupling[35] have improved the breakdown values up to 200V only. As discussed in chapter 1, GaN because of its higher critical electric field will result in lower on-resistance and can simultaneously operate at voltages >400 V.

In this chapter, the basic structure of Schottky diode is introduced. Then a discussion of the principle of the metal-semiconductor junction is provided, followed by a state of the art review of various Schottky diodes reported in the literature to date.

#### 2.2 Schottky Rectifier

Nonlinear current flow across a metal-semiconductor contact has been known for a long time. Walter Schottky in 1938, explained the way specific combination of metals and semiconductors can rectify current.

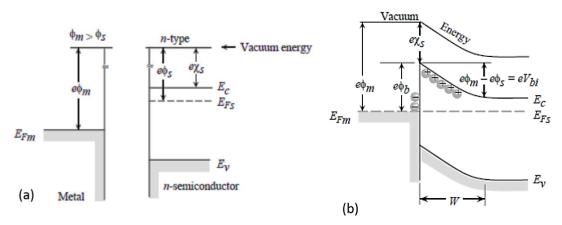

A Schottky diode junction is formed by depositing a metal with high work function (typically by evaporation or sputtering under vacuum) onto a wafer that has been doped either ntype or p-type. In the case of GaN <u>due</u> to the presence of background impurities, GaN intrinsically acts like n-doped material. Figure 2-1 illustrates the energy bandgap of metal and an n-type semiconductor.

**Figure 2-1**: Energy band diagram for a metal and semiconductor (a) in isolation (b) after making and electrical connection [96]

When metal is brought into contact with an n-type semiconductor, electrons diffuse into the metal until thermal equilibrium is established. This transfer of electrons leaves positive charges within a depletion region as shown in the figure 2-1. The depletion region formed at the surface of the semiconductor supports the entire contact potential. The internal voltage difference between metal and semiconductor is referred as the built-in potential( $V_{bi}$ ).

The Schottky barrier height ( $\varphi_B$ ) is related to built-in potential by

$$\varphi_{\rm B} = qV_{\rm bi} + (E_{\rm C} - E_{\rm FS})$$

(2-1)

$$\varphi_{\rm B} = \varphi_{\rm M} - X_{\rm S} \tag{2-2}$$

$\phi_M$ : work function of metal  $X_S$ : electron affinity of semiconductor

The built-in potential creates a zero-bias depletion region within the semiconductor, whose width is given by Eq 2-3

$$W_0 = \sqrt{\frac{2\varepsilon_S V_{bi}}{qN_D}}$$

(2-3)

#### 2.2.1 Forward Conduction

When a positive voltage is applied to the metal, the depletion width decreases, the builtin potential reduces, and current flows across the junction by transport of electrons from the semiconductor to the metal over the barrier. This current is referred to as thermionic emission current [36], and these thermionic emission currents are the most dominant mode of current flow in the Schottky power diodes.

Unlike, p-n junction diodes, the injection of minority carriers is negligible. In a power Schottky rectifiers, the barrier height is intentionally reduced to lower the on-voltage drop making the minority carrier current small. Therefore, if the forward voltage is removed, the current stops within a few picoseconds and reverse voltage can be established. Thus, there is no delay effect due to charge storage as in p-n junction diodes.

Also, in a power rectifier the doping concentration is relatively low to block the high reverse voltage. This spreads the depletion region over a substantial distance. Consequently, the potential barrier is not sharp enough to allow significant current via tunneling.

The thermionic emission current flow across the Schottky barrier interface is given by Eq 2-4

$$J = AT^2 e^{-(q\varphi_{BN}/kT)} \left[ e^{(qV/kT)} - 1 \right]$$

(2-4)

Where A is the effective Richardson's constant, T is the absolute temperature, k is the Boltzmann's constant, and V is the applied bias. The Richardson's constant value for GaN in the literature spans from  $3.23 \times 10^{-5}$  to  $26 \text{ Acm}^{-2}\text{K}^{-2}[37-39]$ . Hacke et al. suggested that this variation in A values was caused by the presence of a barrier through which the electron must tunnel[40]. Guo et al. suggested that the decrease of the effective contact area may also cause the low value of A\*[41].

When a forward bias is applied across the two terminals, the first term in the square brackets of the equation becomes more dominant, resulting in forward current density given by

$$J_F = \mathrm{AT}^2 \mathrm{e}^{-(\mathrm{q}\varphi_{\mathrm{BN}}/\mathrm{kT})} \,\mathrm{e}^{(\mathrm{q}V_{\mathrm{FS}}/\mathrm{kT})} \tag{2-5}$$

Where  $V_{FS}$  is the voltage drop across the Schottky contact. In the case of power Schottky rectifiers, to support high reverse blocking voltages, lightly doped drift regions are used. As a result, there is an additional voltage drop across the drift layer ( $V_R$ ), which increases the voltage drop across Schottky contact further. The on-state voltage drop ( $V_F$ ) for a power Schottky rectifier, after including the resistive voltage drops, is given by

$$V_F = V_{FS} + V_R \tag{2-6}$$

$$V_{\rm F} = \frac{kT}{q} \ln \left[ \frac{J_{\rm F}}{J_{\rm S}} \right] + R_{\rm S,SP} J_{\rm F} \qquad (2-7)$$

$$J_{\rm S} = AT^2 e^{-(q\varphi_{\rm BN}/kT)}$$

(2-8)

# $$\begin{split} &J_F: Forward \ current \ density \\ &J_S: Saturation \ current \ dnsity \\ &R_{S,SP}: Total \ series \ specific \ resistance \end{split}$$

The total series specific resistance  $(R_{S, SP})$  is determined by the diode structure, and is discussed in detail in section 2.3

#### 2.2.2 Reverse blocking

When a reverse bias is applied, the depletion region extends into the lightly doped semiconductor. The voltage is supported across the drift region with the maximum electric field located at the metal semiconductor junction. The Poisson's equation for the n- region is then given by

$$\frac{d^2V}{dx^2} = -\frac{dE}{dx} = -\frac{Q(x)}{\varepsilon_s} = \frac{qN_D}{\varepsilon_s}$$

(2-9)

Where Q(x) is charge within depletion region due to the ionized donors,  $\boldsymbol{\epsilon}_s$  is dielectric constant for the semiconductor and  $N_D$  is the donor concentration of the drift region. Integrating Eq 2-9 provides the electric field distribution

$$E(x) = \frac{qN_D}{\varepsilon_s}(W_D - x)$$

The maximum electric field is at the interface i.e., x=0

$$E_{M} = \frac{qN_{D}}{\varepsilon_{s}} (W_{D}) \qquad (2-10)$$

$$W_{D} = \sqrt{\frac{2\varepsilon_{S}V_{a}}{qN_{D}}} \qquad (2-11)$$

$$E_{M} = \sqrt{\frac{2qN_{D}V_{a}}{\varepsilon_{S}}} \qquad (2-12)$$

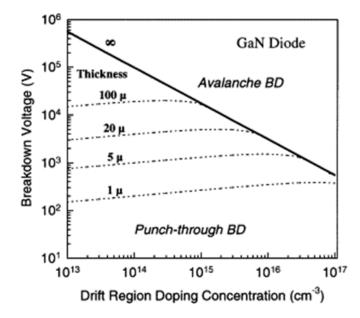

When the applied voltage increases, the maximum electric field increases, resulting in the acceleration of carriers at higher velocities. With further increase in electric field, carriers gain sufficient kinetic energy so that their interaction with lattice generates more charge carriers. These charge carriers further gain momentum from the high electric field in the drift region and will further multiply the charge carriers through impact ionization. Consequently, impact ionization results in high current flow leading to avalanche breakdown of the diode. The maximum electric field before which the diode undergoes breakdown is referred to as critical electric field of the semiconductor. From Eq 2-12, it is evident that the breakdown voltage is inversely related to doping concentration. Therefore, drift regions are preferred with lower doping concentration to sustain higher voltages in the reverse bias. Figure 2-2 illustrates the relationship between doping concentration and the breakdown voltage in GaN.

Figure 2-2: Break down Vs. drift region doping concentration of GaN [11]

However, in forward bias lower doping results in higher on-resistance which is not desirable. As increased on-resistance leads to increase in conduction losses. Therefore, there is a tradeoff between on-resistance and breakdown voltage of a diode.

### 2.3 Material systems

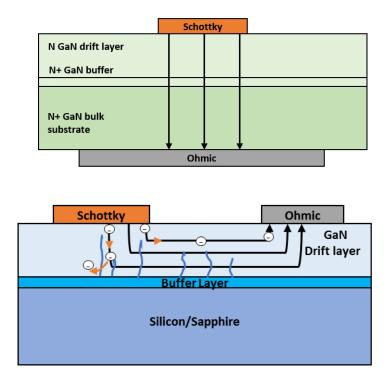

Schottky diodes primarily can be classified into vertical and lateral geometry depending on the type of the substrate.

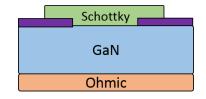

#### 2.3.1 Vertical diodes

Vertical diodes are comprised of a lightly doped drift layer grown on a highly conducting GaN bulk substrate. A Schottky rectifier formed at metal and epilayer interface and an ohmic contact is formed on the back side of the conducting substrate. So, current flows through the epilayer, buffer, and substrate as shown in figure 2-3. Thus, there is additional potential drop across the drift layer (I\*Repi), bulk substrate (I\*Rsub) and ohmic contact(I\*Rc). The resistance contributed by the substrate must be included in analysis because it can be comparable with that of the drift region [42]. Resistance due to the epilayer depends on the width, mobility and doping concentration. Resistance due to the substrate depends on the thickness and resistivity of the bulk substrate as shown in below Eq 2-14 & 2-15.

$$R_{ON} = R_{epi} + R_{sub} + R_C \qquad (2-13)$$

$$R_{epi} = \frac{W_d}{qu_n N_d} = \frac{4 V_{BD}^2}{\epsilon_s \mu_n E_C^3}$$

(2-14)

$$R_{sub} = \rho_{sub} * d$$

(2-15)

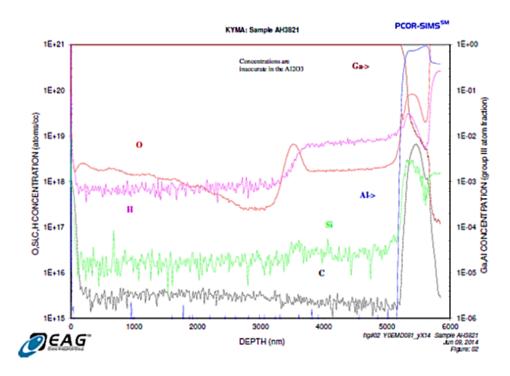

To block higher voltages across the drift layer, vertical geometry is preferred over the lateral due to less scattering of electrons and absence of leakage currents at the epilayer and substrate interface. These factors are discussed in detail in the following section. The most common vertical device uses an unintentionally doped epilayers are grown using MOVPE or MOCVD[43] on a free-standing bulk HVPE substrate [44]. Both the MOCVD and MOVPE growth techniques result in high background impurity concentrations of carbon(c), oxygen (O) and hydrogen (H). These impurities occupy Ga site and form shallow donor states near the band edge resulting in increase in the leakage currents across the junction in the reverse bias. To reduce the background impurities, recently HVPE has been used to grow the epilayer on HVPE bulk

substrates. However, these diodes have inferior breakdown values compared to films grown by MOCVD or MOVPE[45].

#### 2.3.2 Lateral diodes

In lateral devices epilayers are grown on heterosubstrates such as Si or sapphire due to the lack of GaN bulk substrates. Usually, epilayers grown on heterosubstrates suffer a highdensity threading dislocation originating at the interface due to mismatch in the lattice parameters. These threading defects propagate along the growth direction, and some reach the surface. Eventually, with the development of a two-step growth technique that uses a lowtemperature buffer prior to the growth of epilayer have improved the quality of epilayer grown on heterosubstrates. In the two step growth, initially buffer film consists of disordered hexagonal islands[46] is grown. Then, the temperature is ramped up to anneal the buffer layer and then to grow the epilayer which decreases defect densities.

The diodes built on these epilayers grown on heterosubstrates have both ohmic and Schottky contact on the top surface of the epilayer. Thus, the current flow is within the drift layer, unlike vertical diode as illustrated in figure 2-3. In forward bias, since the current is no longer flowing through the substrate, the only factors contributing to forward resistance are the epilayer resistance and the contact resistance. Since the substrate resistance is absent in lateral diodes, the on-resistance is expected to be lower than in the vertical devices. However, it was observed that threading defects that propagate along the growth direction are normal to the current flow (blue lines in figure 2-3), trap the free flow of electrons laterally. Also, these defects are reported to scatter the electrons and thereby increase the on-resistance.

$$R_{ON} = R_{epi} + R_C \tag{2-16}$$

$$R_{epi} = \frac{W_d}{qu_n N_d} = \frac{4 V_{BD}^2}{\epsilon_S \mu_n E_C^3}$$

(2-17)

Lateral diodes do not show consistent properties due to the presence of a high number defects that are randomly distributed across the film. Also, these diodes are limited to lower voltage applications. Especially, when GaN layers are grown on conducting substrates such as Si, with the increase in bias voltage, the depletion width extends deeper into the epilayer, reaching the GaN and buffer interface. Since silicon is conducting, when the space charge region reaches the silicon interface, it causes additional conduction along the interface.

Figure 2-3: Current flow in vertical device and in lateral device

#### 2.4 Literature review

In this section, various kinds of Schottky diodes reported in the literature from 1999 to present are discussed. As mentioned earlier, for a Schottky diode the two critical parameters to evaluate the performance are the on-resistance in the forward bias and the breakdown voltage in the reverse bias. For the following diodes, these two values are presented. Also, the factors such a drift layer thickness, donor concentration, defect densities that affect the diode characteristics are also summarized.

As stated before due to lack of a bulk substrates, diodes initially used drift layers grown on heterosubstrates. Bandic et al., used 8-10 um thick hydride vapor phase epitaxy grown GaN on a sapphire substrate to fabricate a Schottky rectifier. A cross-sectional transmission electron microscopy (XTEM) study of their HVPE films showed that the region adjoining the interface was highly disordered and included several subgrain boundaries, stacking faults and prismatic plane fault. The electron concentrations and mobilities at the thin interface and at the top surface layer were 2x10<sup>20</sup> cm<sup>-3</sup> and 35 cm<sup>2</sup>/Vs, and 2x10<sup>16</sup> cm<sup>-3</sup> and 265 cm<sup>2</sup>/Vs, respectively. These values correspond to conductivities of 1120 and 0.85 S cm-1 for the interface layer and the surface layer, indicating that the interface layer is approximately three times more conductive. The authors tested lateral geometries with standard circular contacts, diodes with field plate overlapping a SiO2 layer, and quasi-vertical diodes with mesa structure as shown in figure 2-4. voltage of 5V. The high on voltages were attributed to low carrier concentration on the surface layers. On the other hand, mesa devices formed by etching away the top 5 um film have resulted in on-voltage of 4.2V at the expense of higher leakage currents due to highly conducting layers near the interface. The best devices were reported to have a current density of 100 A/cm2 at voltage of 4.2 V at a and a saturation current density of  $10^{-5}$  A/cm2 at a reverse bias of 100 V[47].

**Figure 2-4**: Schematic of GaN Schottky rectifier built from HVPE grown layers on sapphire. (a) lateral diode (b) mesa diode (c) lateral diode with a field plate extending over SiO2[47]

Dang et al., used films grown by MOCVD on c-plane sapphire to fabricate Schottky diodes. Two types of MOCVD films (i) 11  $\mu$ m unintentionally doped GaN was grown using 1  $\mu$ m n+ doped GaN as a buffer (ii) and a 3  $\mu$ m thick highly resistive layer was grown using 300A<sup>0</sup> novel buffer. The carrier concentration of a 11 $\mu$ m and 3  $\mu$ m epilayers were 2x10<sup>16</sup> and  $\leq$ 10<sup>15</sup> respectively. The low carrier concentration in 3um layers was attributed to a novel buffer. Mesa devices were built using 11um layers by etching the GaN layer with the ohmic contacts deposited on the n+ layer and Schottky contacts on top of the mesa. A standard circular ohmic and Schottky contacts are made on 3um GaN without any etching. A breakdown value of 550V and 2000V

were reported using 11um (nominal buffer) and 3um (modified buffer). The on-resistance of the mesa devices was three orders lower than the planar diodes. Authors also tested the diodes made on films grown by HVPE and MBE techniques and obtained the highest breakdown of 200V and 80V as listed in table 2-1.

| Method          | Thickness(µm) | Doping(cm <sup>-3</sup> ) | V <sub>BD</sub> (V) |

|-----------------|---------------|---------------------------|---------------------|

| HVPE            | 60-100        | 2x10 <sup>17</sup>        | 60-200              |

| MBE             | 2-5           | 5x10 <sup>16</sup>        | 60-80               |

| MOCVD(nominal)  | 5-12          | 2x10 <sup>16</sup>        | 350-550             |

| MOCVD(modified) | 3             | <b>≤</b> 10 <sup>15</sup> | 2000                |

Table 2-1:

Drift layer thickness, doping concentration and breakdown voltages of the

diodes built on films grown by HVPE, MBE, MOCVD (nominal buffer) and MOCVD (modified

buffer)[48]

Later, with the development of HVPE bulk substrates, Johnson et al., used HVPE bulk substrates that are separated from sapphire using laser beam heating. Then an unintentionally doped GaN layer with about 6 $\mu$ m thickness were deposited using MOCVD. Schottky diodes built from these layers with carrier concentration of 5x10<sup>16</sup> cm<sup>-3</sup> were reported to have a breakdown of 450V and on-resistance value of 20 m $\Omega$ .cm<sup>2</sup> [49].

K.Ip et al., reported Schottky diodes built on bulk HVPE crystals with a standard field and damage implants as shown in figure 2-5 and compared to simulated values. A 75um diameter diode displayed a breakdown voltage of 120V while the simulations predicted a higher breakdown of 600V. The disparity between the theoretical and experimental values was ascribed to crystal defects such as micropipes and dislocations that initiate carrier multiplication resulting in the premature failure of the diode.

**Figure 2-5:** Schematic of Schottky rectifier fabricated on free-standing GaN with field termination [50]

Zou et al. used 10 mm x 10 mm HVPE bulk substrates of 450 $\mu$ m thickness without epitaxial layers provided by Kyma Technologies, with a doping level of 7x10<sup>15</sup> cm<sup>-3</sup> and a defect density of 10<sup>6</sup> cm<sup>-2</sup>. Pt Schottky diodes with different diameters (50um, 150u, 300um), without field termination, were built and tested. An average breakdown value of 630V, 600V and 220V were reported for 50um,150um, and 300um diodes. Also, the 50um diode offered a low on resistance of 2.2 m $\Omega$ -cm<sup>-2</sup>.

Hashimoto et al. compared the quality of films grown using MOVPE on a low defective HVPE bulk substrate (10<sup>6</sup> cm<sup>-2</sup>) and a sapphire substrate with a GaN buffer. Both the films were grown under similar conditions. However, films grown on a sapphire substrate using buffer layers were rough with the several pits on the surface. Also, they have higher C, O and H impurities and higher defects. Authors speculated higher background impurities due to accumulation of impurities on the surface of the defect pits. Figure 2-6 shows the dependence of the impurity concentration on the defect density

Figure 2-6: Dependence of impurity concentration on the defect density[51]

Schottky barrier diodes built on bulk substrate were reported to have the breakdown voltage of 580V and on-resistance of 1.3 m $\Omega$ -cm<sup>-2</sup>. The lateral diodes built on sapphire showed higher leakage currents and a lower breakdown voltage of 163V. The on-resistance values were much higher on the order of 14.4 mOhms-cm<sup>-2</sup> in lateral diodes and was associated to the poor quality of the drift layer even after using a buffer layer.

Lu et al. developed a vertical GaN Schottky rectifier on a freestanding bulk GaN substrate by employing homoepitaxial growth technique. The n-/n+ epilayers were grown on a HVPE bulk GaN substrate by metal-organic chemical vapor deposition. The dislocation density of the epitaxial layer determined by cathodoluminescence mapping technique was  $6 \times 10^6$  cm<sup>-2</sup>.

The surface roughness was reported to be less than 1 nm. The SIMS data showed Si carrier concentration of  $6x10^{16}$  cm<sup>-3</sup> in the drift layers. The Schottky rectifiers used standard field termination as shown in figure 2-7. Low leakage current of  $3x10^{-8}$ A at -100 V was recorded due to low dislocation density in the epilayer. The reverse breakdown voltage for these diodes was defined at the reverse current level of 0.1 A/cm2, and the breakdown values down values were distributed between 260 to 430 V[52].

Figure 2-7: Schematic of vertical Schottky rectifier fabricated on bulk GaN substrate[52]

Saitoh et al. reported diodes with efficiency closest to ideal values for the first time in 2010. HVPE produced GaN substrates were used to build Schottky rectifiers with threading dislocation densities  $< 1 \times 10^6$  cm<sup>-2</sup> and have exhibited n-type conductivity with resistivity value as low as .01  $\Omega$ cm. A 5  $\mu$ m epitaxial layer was deposited on top of the bulk substrate using MOCVD[53] with Si concentration of  $8 \times 10^{15}$  cm<sup>-3</sup>. 1  $\mu$ m thick PECVD deposited SiN<sub>x</sub> was used as the dielectric layer, and the field plate structure was formed by Schottky contact overlapped

with dielectric as illustrated in the figure 2-8. The breakdown voltage and the specific onresistance of these Schottky barrier diodes were 1100V and 0.71 m $\Omega$ .cm<sup>2</sup> and respectively.

Figure 2-8: Schottky rectifier structure with the field plate reported by Saitoh et al.[53]

The electron mobility in these drift layer was reported to be 930cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, which is close to theoretically predicted value[54]<sup>-</sup> There were several other groups, who also used MOCVD to deposit the epitaxial layer. However, the mobility values reported by Saitoh are the optimum by far.

J.Suda et al., have tested 3 different bulk HVPE samples without a field termination and an epilayer. Doping of the substrates varied from  $10^{16}$  to  $2x10^{17}$  cm<sup>-3</sup> and the dislocation densities were estimated to be 2-3 x  $10^{6}$  cm<sup>-2</sup>. They reported an increase in leakage currents with the increased doping concentration as illustrated in the figure 2-6.

**Figure 2-9:** Reverse I-V characteristics of GaN Schottky barrier diodes with different donor concentration of 7.6 x  $10^{15}$ , 7.9 x  $10^{16}$  and 1.4 x  $10^{17}$  cm<sup>-3</sup> [55]

Obzek et al., implemented argon implantation at the contact edge to passivate the high electric fields at the contact periphery. Diodes fabricated on n-type doped layers (10<sup>14</sup> cm<sup>-3</sup>) grown by MOCVD on a bulk substrate have resulted in a breakdown voltage of 300V. With the edge termination, the breakdown value increased to1650V[56]. Compared to field plate architecture reported by Saitoh, diode with argon implantation have a higher breakdown, but the leakage currents are almost 3-4 orders higher.

There were several other diodes reported in the literature that used bulk HVPE. The growth conditions were varied, and different doping concentration were produced and tested [42, 57]. The break down showed a dependence on the carrier concentration, with the samples having low doping exhibiting a higher breakdown and the on-resistance values also showed dependence on doping concentration and the thickness of the bulk substrate.

The on-resistance vs. breakdown values for all the diodes that were discussed in this section are plotted in the figure 2-7. The green squares correspond to the diodes that are built either on bulk HVPE substrate or epilayers grown on HVPE substrate, and the orange squares represent diodes that used epilayers grown on heterosubstrates such as Si or sapphire. Solid blue yellow, dotted blue and red lines correspond to Si, GaN, Ga2O3, and diamond materials theoretical limit. Most of the didoes have on-resistance and the breakdown values higher than the standard Si, however they are still far below the GaN theoretical limit.

Figure 2-10: On resistance Vs. Breakdown voltages for Schottky rectifiers reported in the literature.

Some Schottky diodes in the literature have used an alloy of GaN with Al to produce AlGaN. The bandgap can then be tuned depending on the Al composition from 3.4 eV to 6.4 eV.

Similar to the GaAs/AlGaAs system, GaN/ AlGaN confines the electrons in 2-dimensional electron gas(DEG), and the mobility of the carriers is predicted to be as high as 2000Vcm-1s-1. AlGaN/GaN is predominantly used for high electron mobility transistors (HEMTs) due to its superior carrier mobility. However, Mignda et al. have used AlGaN/GaN grown on Si to build a Schottky diode, and have used multiple field plate structure for uniform field distribution at the contact edges. This device design has exhibited a breakdown voltage of 1900V with an on resistance of 5.12 m $\Omega$ -cm<sup>2</sup>. Since this work is more focused on GaN diodes, GaN/AlGaN is not discussed in detail here. Moving to back to GaN material systems.

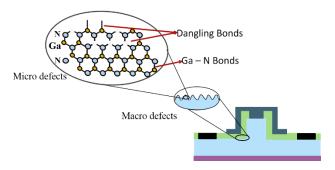

Among the various growth techniques that were discussed so far, HVPE has evolved so much in the last decade, that its free-standing bulk substrate use in power devices have become ubiquitous. Also, these substrates are grown commercially by vendors such as Kyma, Agnitron, Structured materials and others. However, field crowding at the edge of the contact and the high background impurity concentration in drift regions that are typically deposited by MOCVD or MOVPE are critical issues that are yet to be addressed to utilize the GaN to its fullest potential.

# 2.5 Field crowding

In an ideal diode structure, electric field is uniformly distributed along the lateral direction, and there are no fringing field issues. However, for a real diode with finite size Schottky and ohmic contacts, the electric field is non-uniform which leads to early device breakdown. The non-uniform electric field is concentrated at the Schottky contact edges. The goal of edge termination techniques is to achieve an electric field distribution as close to the ideal

case as possible. A number of edge modification techniques have been used in the literature, such as field plates[53], damage implants[56], guard rings[33], and different combinations of these strategies[58-60], as shown in figure 2-11. In a field plate structure, the Schottky contact extends over the dielectric. This extended contact acts like a freestanding metal-insulator-semiconductor (MIS) electrode and distributes the field away from the contact periphery along the epitaxial layer surface. Damage implant techniques use high dose ion implantation to create defects located near the mid-band gap of GaN. These implants create a high resistive layer at the diode edge and promote the spreading of potential along the surface, resulting in reduced edge electric field. Guard ring techniques, like damage implants, use p-type implants instead of damage implants to deflect the field along floating p-n junctions.

**Figure 2-11**: Common field termination techniques (i) field plate design (ii) damage implant(iii) guard-ring using p implants

In all edge techniques overviewed thus far, the breakdown is still below the expected ideal diode breakdown voltage because some amount of field crowding still occurs.

# **CHAPTER 3 SIMULATIONS**

This chapter presents the simulations used in the development of a novel wraparound field plate structure, that promotes uniform field distribution across the active device area by confining high intensity fields in the dielectric and thereby improving the breakdown voltages. It also studies the effect of various geometrical aspects on device performance. Breakdown characteristics for an ideal diode, a real diode with finite contact length and a conventional field plate technique used in the literature are simulated and compared to the novel wraparound field plate.

#### 3.1 Introduction

We present our new wrap-around field plate structure[61] that surrounds the active device area along with the conventional field plate structure and compare the breakdown voltages. Also, we study the factors that affect the device performance.

A standard field plate technique(refer to figure 2-1) is chosen for efficiency comparisons with the proposed wraparound. The standard field plate technique exhibited higher efficiencies in terms of breakdown values among the various field termination techniques reported in literature till date. It also has the added benefit of being the easiest to build among all the reported field termination techniques. The standard field plate structure involves no ion implantation, unlike other techniques, which need to be carried out under controlled conditions. If not, higher energy ions tend to travel to bulk of the semiconductor and knock the Ga, N atoms out of the lattice and create defects. These knocked out free atoms will further collide with other atoms in the lattice causing impact ionization. Thus, the standard field plate in which Schottky contact is extended over the deposited dielectric is the more often chosen technique as it does not create additional defects during device fabrication resulting in comparatively improved breakdown characteristics than other device structures.

#### 3.2 Simulation

Silvaco tool, DevEdit was used to define the device geometry parameters, such as thickness and carrier concentration for the substrate, buffer layer and epitaxial layer. Materialspecific constants such as bandgap, dielectric constant, density of states, intrinsic carrier concentration, mobilities and lattice constants (shown in table 3-1) are taken from literature for Wurtzite GaN and are used in the code. However, as the GaN is far from being mature as an electronic semiconductor material, it is not rare to find discrepancies between the theoretically calculated material properties and those that are experimentally measured. (The complete code for various device architectures used in this study is available in the appendix).

| Parameter                                                               | GaN                     | Units               |

|-------------------------------------------------------------------------|-------------------------|---------------------|

| Band gap                                                                | 3.42                    | eV                  |

| Lattice constant                                                        | 3.189                   |                     |

| Critical Electric Field (E <sub>c</sub> )                               | 3.75                    | MV/cm               |

| Hole life time(auger)                                                   | 1e-9                    | S                   |

| Electron life time(auger)                                               | 1e-9                    | S                   |

| Valence band effective density of states@ $300K(N_v)$                   | 4.6 x 10 <sup>19</sup>  | cm <sup>-3</sup>    |

| Conduction band effective<br>density of states @ 300k (N <sub>c</sub> ) | 2.3 x 10 <sup>18</sup>  | cm <sup>-3</sup>    |

| Intrinsic carrier<br>concentration(n <sub>i</sub> )                     | 2.9 x 10 <sup>-9</sup>  | cm <sup>-3</sup>    |

| Dielectric                                                              | 8.9                     |                     |

| Peak velocity                                                           | 2.2 x 10 <sup>7</sup>   | cm/s                |

| Saturation Velocity                                                     | 1.125 x 10 <sup>7</sup> | cm/s                |

| Hole mobility                                                           | 10                      | cm <sup>2</sup> /Vs |

| Electron mobility                                                       | 525                     | cm <sup>2</sup> /Vs |

| Donor energy level                                                      | 0.016                   | eV                  |

| Acceptor energy level                                                   | 0.175                   | eV                  |

Table 3-1 Material parameters used in GaN Schottky diode simulation[62-64]

Device simulations were carried out using Silvaco ATLAS. Special models such as field dependent mobility (FLDMOB), concentration dependent mobility (CONMOB), bandgap narrowing (BGN), Shockley Read Hall (SRH) and auger recombination (AUGER) were used to simulate the Schottky diode.

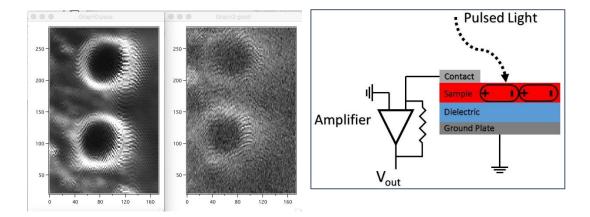

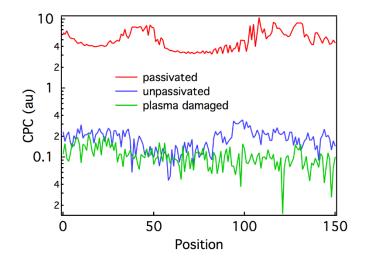

#### **3.2.1 IDEAL DIODE SIMULATIONS**